4422 lines

155 KiB

C

4422 lines

155 KiB

C

/**

|

|

* @file ad5940.c

|

|

* @brief AD5940 library. This file contains all AD5940 library functions.

|

|

* @author ADI

|

|

* @date March 2019

|

|

* @par Revision History:

|

|

*

|

|

* Copyright (c) 2017-2019 Analog Devices, Inc. All Rights Reserved.

|

|

*

|

|

* This software is proprietary to Analog Devices, Inc. and its licensors.

|

|

* By using this software you agree to the terms of the associated

|

|

* Analog Devices Software License Agreement.

|

|

**/

|

|

#include "ad5940.h"

|

|

|

|

/*! \mainpage AD5940 Library Introduction

|

|

*

|

|

*

|

|

*

|

|

* # Introduction

|

|

*

|

|

* The documentation is for AD594x library and examples.

|

|

*

|

|

* # Manual Structure

|

|

*

|

|

* @ref AD5940_Library

|

|

* - @ref AD5940_Functions

|

|

* - @ref TypeDefinitions

|

|

* @ref AD5940_Standard_Examples

|

|

* @ref AD5940_System_Examples

|

|

*

|

|

* # How to Use It

|

|

* We provide examples that can directly run out of box.

|

|

* The files can generally be separated to three parts:

|

|

* - AD5940 Library files. ad5940.c and ad5940.h specifically. These two files are shared among all examples.

|

|

* - AD5940 System Examples. The system examples mean system level application like measuring impedance.

|

|

* - Standard examples. These include basic block level examples like ADC. It shows how to setup and use one specific block.

|

|

*

|

|

* ## Requirements to run these examples

|

|

* ### Hardware

|

|

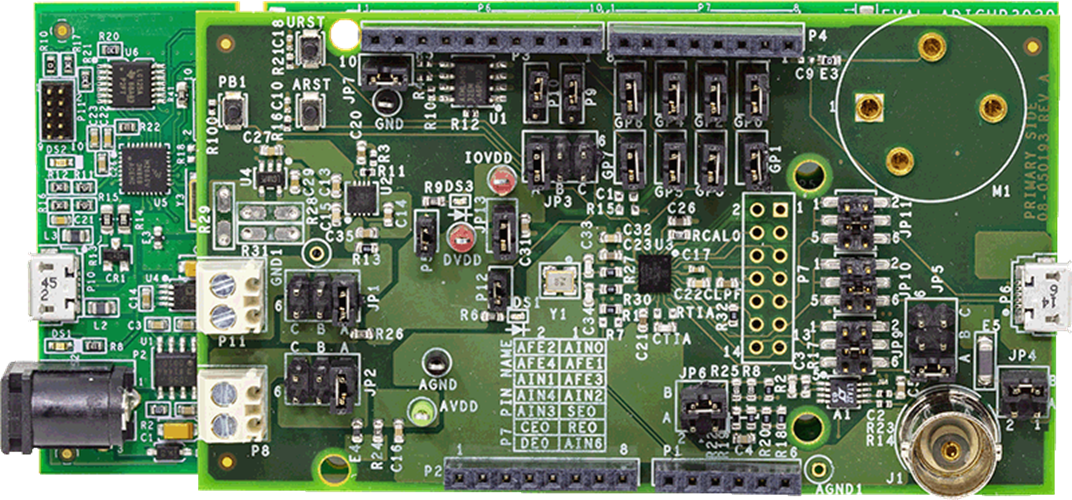

* - Use EVAL_AD5940 or EVAL_AD5941. The default MCU board we used is ADICUP3029. We also provide project for ST NUCLEO board.

|

|

* - Or use EVAL_ADuCM355

|

|

* ### Software

|

|

* - Pull all the source file from [GitHub](https://github.com/analogdevicesinc/ad5940-examples.git)

|

|

* - CMSIS pack that related to specific MCU. This normally is done by IDE you use.

|

|

*

|

|

* ## Materials

|

|

* Please use this library together with following materials.

|

|

* - [AD5940 Data Sheet](https://www.analog.com/media/en/technical-documentation/data-sheets/AD5940.pdf)

|

|

* - [AD5940 Eval Board](https://www.analog.com/en/design-center/evaluation-hardware-and-software/evaluation-boards-kits/EVAL-AD5940.html)

|

|

*

|

|

*/

|

|

|

|

/* Remove below variables after AD594x is released. */

|

|

static BoolFlag bIsS2silicon = bFALSE;

|

|

|

|

/* Declare of SPI functions used to read/write registers */

|

|

#ifndef CHIPSEL_M355

|

|

static uint32_t AD5940_SPIReadReg(uint16_t RegAddr);

|

|

static void AD5940_SPIWriteReg(uint16_t RegAddr, uint32_t RegData);

|

|

#else

|

|

static uint32_t AD5940_D2DReadReg(uint16_t RegAddr);

|

|

static void AD5940_D2DWriteReg(uint16_t RegAddr, uint32_t RegData);

|

|

#endif

|

|

|

|

/**

|

|

* @addtogroup AD5940_Library

|

|

* The library functions, structures and constants.

|

|

* @{

|

|

* @defgroup AD5940_Functions

|

|

* @{

|

|

* @defgroup Function_Helpers

|

|

* @brief The functions with no hardware access. They are helpers.

|

|

* @{

|

|

* @defgroup Sequencer_Generator_Functions

|

|

* @brief The set of function used to track all register read and write once it's enabled. It can translate register write operation to sequencer commands.

|

|

* @{

|

|

*/

|

|

|

|

#define SEQUENCE_GENERATOR /*!< Build sequence generator part in to lib. Comment this line to remove this feature */

|

|

|

|

#ifdef SEQUENCE_GENERATOR

|

|

/**

|

|

* Structure used to store register information(address and its data)

|

|

* */

|

|

typedef struct

|

|

{

|

|

uint32_t RegAddr :8; /**< 8bit address is enough for sequencer */

|

|

uint32_t RegValue :24; /**< Reg data is limited to 24bit by sequencer */

|

|

}SEQGenRegInfo_Type;

|

|

|

|

/**

|

|

* Sequencer generator data base.

|

|

*/

|

|

struct

|

|

{

|

|

BoolFlag EngineStart; /**< Flag to mark start of the generator */

|

|

uint32_t BufferSize; /**< Total buffer size */

|

|

|

|

uint32_t *pSeqBuff; /**< The buffer for sequence generator(both sequences and RegInfo) */

|

|

uint32_t SeqLen; /**< Generated sequence length till now */

|

|

SEQGenRegInfo_Type *pRegInfo; /**< Pointer to buffer where stores register info */

|

|

uint32_t RegCount; /**< The count of register info available in buffer *pRegInfo. */

|

|

AD5940Err LastError; /**< The last error message. */

|

|

}SeqGenDB; /* Data base of Seq Generator */

|

|

|

|

/**

|

|

* @brief Manually input a command to sequencer generator.

|

|

* @param CmdWord: The 32-bit width sequencer command word. @ref Sequencer_Helper can be used to generate commands.

|

|

* @return None;

|

|

*/

|

|

void AD5940_SEQGenInsert(uint32_t CmdWord)

|

|

{

|

|

uint32_t temp;

|

|

temp = SeqGenDB.RegCount + SeqGenDB.SeqLen;

|

|

/* Generate Sequence command */

|

|

if(temp < SeqGenDB.BufferSize)

|

|

{

|

|

SeqGenDB.pSeqBuff[SeqGenDB.SeqLen] = CmdWord;

|

|

SeqGenDB.SeqLen ++;

|

|

}

|

|

else /* There is no buffer */

|

|

SeqGenDB.LastError = AD5940ERR_BUFF;

|

|

}

|

|

|

|

/**

|

|

* @brief Search data-base to get current register value.

|

|

* @param RegAddr: The register address.

|

|

* @param pIndex: Pointer to a variable that used to store index of found register-info.

|

|

* @return Return AD5940ERR_OK if register found in data-base. Otherwise return AD5940ERR_SEQREG.

|

|

*/

|

|

static AD5940Err AD5940_SEQGenSearchReg(uint32_t RegAddr, uint32_t *pIndex)

|

|

{

|

|

uint32_t i;

|

|

|

|

RegAddr = (RegAddr>>2)&0xff;

|

|

for(i=0;i<SeqGenDB.SeqLen;i++)

|

|

{

|

|

if(RegAddr == SeqGenDB.pRegInfo[i].RegAddr)

|

|

{

|

|

*pIndex = i;

|

|

return AD5940ERR_OK;

|

|

}

|

|

}

|

|

return AD5940ERR_SEQREG;

|

|

}

|

|

|

|

/**

|

|

* @brief Get the register default value by SPI read. This function requires AD5940 is in active state, otherwise we cannot get the default register value.

|

|

* @param RegAddr: The register address.

|

|

* @param pRegData: Pointer to a variable to store register default value.

|

|

* @return Return AD5940ERR_OK.

|

|

*/

|

|

static AD5940Err AD5940_SEQGenGetRegDefault(uint32_t RegAddr, uint32_t *pRegData)

|

|

{

|

|

#ifdef CHIPSEL_M355

|

|

*pRegData = AD5940_D2DReadReg(RegAddr);

|

|

#else

|

|

*pRegData = AD5940_SPIReadReg(RegAddr);

|

|

#endif

|

|

return AD5940ERR_OK;

|

|

}

|

|

|

|

/**

|

|

* @brief Record the current register info to data-base. Update LastError if there is error.

|

|

* @param RegAddr: The register address.

|

|

* @param RegData: The register data

|

|

* @return Return None.

|

|

*/

|

|

static void AD5940_SEQRegInfoInsert(uint16_t RegAddr, uint32_t RegData)

|

|

{

|

|

uint32_t temp;

|

|

temp = SeqGenDB.RegCount + SeqGenDB.SeqLen;

|

|

|

|

if(temp < SeqGenDB.BufferSize)

|

|

{

|

|

SeqGenDB.pRegInfo --; /* Move back */

|

|

SeqGenDB.pRegInfo[0].RegAddr = (RegAddr>>2)&0xff;

|

|

SeqGenDB.pRegInfo[0].RegValue = RegData&0x00ffffff;

|

|

SeqGenDB.RegCount ++;

|

|

}

|

|

else /* There is no more buffer */

|

|

{

|

|

SeqGenDB.LastError = AD5940ERR_BUFF;

|

|

}

|

|

}

|

|

|

|

/**

|

|

* @brief Get current register value. If we have record in data-base, read it. Otherwise, return the register default value.

|

|

* @param RegAddr: The register address.

|

|

* @return Return register value.

|

|

*/

|

|

static uint32_t AD5940_SEQReadReg(uint16_t RegAddr)

|

|

{

|

|

uint32_t RegIndex, RegData;

|

|

|

|

if(AD5940_SEQGenSearchReg(RegAddr, &RegIndex) != AD5940ERR_OK)

|

|

{

|

|

/* There is no record in data-base, read the default value. */

|

|

AD5940_SEQGenGetRegDefault(RegAddr, &RegData);

|

|

AD5940_SEQRegInfoInsert(RegAddr, RegData);

|

|

}

|

|

else

|

|

{

|

|

/* return the current register value stored in data-base */

|

|

RegData = SeqGenDB.pRegInfo[RegIndex].RegValue;

|

|

}

|

|

|

|

return RegData;

|

|

}

|

|

|

|

/**

|

|

* @brief Generate a sequencer command to write register. If the register address is out of range, it won't generate a command.

|

|

* This function will also update the register-info in data-base to record current register value.

|

|

* @param RegAddr: The register address.

|

|

* @param RegData: The register value.

|

|

* @return Return None.

|

|

*/

|

|

static void AD5940_SEQWriteReg(uint16_t RegAddr, uint32_t RegData)

|

|

{

|

|

uint32_t RegIndex;

|

|

|

|

if(RegAddr > 0x21ff)

|

|

{

|

|

SeqGenDB.LastError = AD5940ERR_ADDROR; /* address out of range */

|

|

return;

|

|

}

|

|

|

|

if(AD5940_SEQGenSearchReg(RegAddr, &RegIndex) == AD5940ERR_OK)

|

|

{

|

|

/* Store register value */

|

|

SeqGenDB.pRegInfo[RegIndex].RegValue = RegData;

|

|

/* Generate Sequence command */

|

|

AD5940_SEQGenInsert(SEQ_WR(RegAddr, RegData));

|

|

}

|

|

else

|

|

{

|

|

AD5940_SEQRegInfoInsert(RegAddr, RegData);

|

|

/* Generate Sequence command */

|

|

AD5940_SEQGenInsert(SEQ_WR(RegAddr, RegData));

|

|

}

|

|

}

|

|

|

|

/**

|

|

* @brief Initialize sequencer generator with specified buffer.

|

|

* The buffer is used to store sequencer generated and record register value changes.

|

|

* The command is stored from start address of buffer while register value is stored from end of buffer.

|

|

* Buffer[0] : First sequencer command;

|

|

* Buffer[1] : Second Sequencer command;

|

|

* ...

|

|

* Buffer[Last-1]: The second register value record.

|

|

* Buffer[Last]: The first register value record.

|

|

* @param pBuffer: Pointer to the buffer.

|

|

* @param BufferSize: The buffer length.

|

|

* @return Return None.

|

|

*/

|

|

void AD5940_SEQGenInit(uint32_t *pBuffer, uint32_t BufferSize)

|

|

{

|

|

if(BufferSize < 2) return;

|

|

SeqGenDB.BufferSize = BufferSize;

|

|

SeqGenDB.pSeqBuff = pBuffer;

|

|

SeqGenDB.pRegInfo = (SEQGenRegInfo_Type*)pBuffer + BufferSize - 1; /* Point to the last element in buffer */

|

|

SeqGenDB.SeqLen = 0;

|

|

|

|

SeqGenDB.RegCount = 0;

|

|

SeqGenDB.LastError = AD5940ERR_OK;

|

|

SeqGenDB.EngineStart = bFALSE;

|

|

}

|

|

|

|

/**

|

|

* @brief Get sequencer command generated.

|

|

* @param ppSeqCmd: Pointer to a variable(pointer) used to store the pointer to generated sequencer command.

|

|

* @param pSeqLen: Pointer to a variable that used to store how many commands available in buffer.

|

|

* @return Return lasterror.

|

|

*/

|

|

AD5940Err AD5940_SEQGenFetchSeq(const uint32_t **ppSeqCmd, uint32_t *pSeqLen)

|

|

{

|

|

AD5940Err lasterror;

|

|

|

|

if(ppSeqCmd)

|

|

*ppSeqCmd = SeqGenDB.pSeqBuff;

|

|

if(pSeqLen)

|

|

*pSeqLen = SeqGenDB.SeqLen;

|

|

|

|

//SeqGenDB.SeqLen = 0; /* Start a new sequence */

|

|

lasterror = SeqGenDB.LastError;

|

|

//SeqGenDB.LastError = AD5940ERR_OK; /* Clear error message */

|

|

return lasterror;

|

|

}

|

|

|

|

/**

|

|

* @brief Start or stop the sequencer generator. Once started, the register write will be recorded to sequencer generator.

|

|

* Once it's disabled, the register write is written to AD5940 directly by SPI bus.

|

|

* @param bFlag: Enable or disable sequencer generator.

|

|

* @return Return None.

|

|

*/

|

|

void AD5940_SEQGenCtrl(BoolFlag bFlag)

|

|

{

|

|

if(bFlag == bFALSE) /* Disable sequence generator */

|

|

{

|

|

SeqGenDB.EngineStart = bFALSE;

|

|

}

|

|

else

|

|

{

|

|

SeqGenDB.SeqLen = 0;

|

|

SeqGenDB.LastError = AD5940ERR_OK; /* Clear error message */

|

|

SeqGenDB.EngineStart = bTRUE;

|

|

}

|

|

}

|

|

|

|

/**

|

|

* @brief Calculate the number of cycles in the sequence

|

|

* @return Return Number of ACLK Cycles that a generated sequence will take.

|

|

*/

|

|

uint32_t AD5940_SEQCycleTime(void)

|

|

{

|

|

uint32_t i, Cycles, Cmd;

|

|

Cycles = 0;

|

|

for(i=0;i<SeqGenDB.RegCount;i++)

|

|

{

|

|

Cmd = (SeqGenDB.pSeqBuff[i] >> 30) & 0x3;

|

|

if (Cmd & 0x2)

|

|

{

|

|

/* A write command */

|

|

Cycles += 1;

|

|

}

|

|

else

|

|

{

|

|

if (Cmd & 0x1)

|

|

{

|

|

/* Timeout Command */

|

|

Cycles += 1;

|

|

}

|

|

else

|

|

{

|

|

/* Wait command */

|

|

Cycles += SeqGenDB.pSeqBuff[i] & 0x3FFFFFFF;

|

|

}

|

|

}

|

|

}

|

|

return Cycles;

|

|

}

|

|

#endif

|

|

/**

|

|

* @} Sequencer_Generator_Functions

|

|

*/

|

|

|

|

/**

|

|

* Check if an uint8_t value exist in table.

|

|

*/

|

|

static int32_t _is_value_in_table(uint8_t value, const uint8_t *table, uint8_t len, uint8_t *index)

|

|

{

|

|

for(int i=0; i<len; i++)

|

|

{

|

|

if(value == table[i])

|

|

{

|

|

*index = i;

|

|

return bTRUE;

|

|

}

|

|

}

|

|

return bFALSE;

|

|

}

|

|

|

|

/**

|

|

* @brief return if the SINC3/SINC2 combination is available for notch 50Hz filter.

|

|

* If it's not availabe, hardware automatically bypass Notch even if it's enabled.

|

|

* @param pFilterInfo the filter configuration, only need sinc2/sinc3 osr and adc data rate information.

|

|

* @return return bTRUE if notch 50Hz filter is available.

|

|

*/

|

|

BoolFlag AD5940_Notch50HzAvailable(ADCFilterCfg_Type *pFilterInfo, uint8_t *dl)

|

|

{

|

|

if((pFilterInfo->ADCRate == ADCRATE_800KHZ && pFilterInfo->ADCSinc3Osr == ADCSINC3OSR_2)||\

|

|

(pFilterInfo->ADCRate == ADCRATE_1P6MHZ && pFilterInfo->ADCSinc3Osr != ADCSINC3OSR_2))

|

|

{

|

|

//this combination suits for filter:

|

|

//SINC3 OSR2, for 800kSPS

|

|

//and SINC3 OSR4 and OSR5 for 1.6MSPS,

|

|

const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_533, ADCSINC2OSR_667,ADCSINC2OSR_800, ADCSINC2OSR_889, ADCSINC2OSR_1333};

|

|

const uint8_t dl_50Hz[] = {15,12,10,9,6};

|

|

uint8_t index;

|

|

if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

|

|

{

|

|

*dl = dl_50Hz[index];

|

|

return bTRUE;

|

|

}

|

|

}

|

|

else if(pFilterInfo->ADCRate == ADCRATE_1P6MHZ && pFilterInfo->ADCSinc3Osr == ADCSINC3OSR_2)

|

|

{

|

|

//this combination suits for filter:

|

|

//SINC3 OSR2 for 1.6MSPS

|

|

const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_889, ADCSINC2OSR_1067, ADCSINC2OSR_1333};

|

|

const uint8_t dl_50Hz[] = {18,15,12};

|

|

uint8_t index;

|

|

if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

|

|

{

|

|

*dl = dl_50Hz[index];

|

|

return bTRUE;

|

|

}

|

|

}

|

|

else if(pFilterInfo->ADCRate == ADCRATE_800KHZ && pFilterInfo->ADCSinc3Osr != ADCSINC3OSR_2)

|

|

{

|

|

//this combination suits for filter:

|

|

//SINC3 OSR4 and OSR5 for 800kSPS,

|

|

const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_178, ADCSINC2OSR_267, ADCSINC2OSR_533, ADCSINC2OSR_640,\

|

|

ADCSINC2OSR_800, ADCSINC2OSR_1067};

|

|

const uint8_t dl_50Hz[] = {18,12,6,5,4,3};

|

|

uint8_t index;

|

|

if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

|

|

{

|

|

*dl = dl_50Hz[index];

|

|

return bTRUE;

|

|

}

|

|

}

|

|

*dl = 0;

|

|

return bFALSE;

|

|

}

|

|

|

|

/**

|

|

* @brief return if the SINC3/SINC2 combination is available for notch 60Hz filter.

|

|

* If it's not availabe, hardware automatically bypass Notch even if it's enabled.

|

|

* @param pFilterInfo the filter configuration, need sinc2/sinc3 osr and adc data rate information.

|

|

* @return return bTRUE if notch 60Hz filter is available.

|

|

*/

|

|

BoolFlag AD5940_Notch60HzAvailable(ADCFilterCfg_Type *pFilterInfo, uint8_t *dl)

|

|

{

|

|

if((pFilterInfo->ADCRate == ADCRATE_800KHZ && pFilterInfo->ADCSinc3Osr == ADCSINC3OSR_2)||\

|

|

(pFilterInfo->ADCRate == ADCRATE_1P6MHZ && pFilterInfo->ADCSinc3Osr != ADCSINC3OSR_2))

|

|

{

|

|

//this combination suits for filter:

|

|

//SINC3 OSR2, for 800kSPS

|

|

//and SINC3 OSR4 and OSR5 for 1.6MSPS,

|

|

const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_667, ADCSINC2OSR_1333};

|

|

const uint8_t dl_60Hz[] = {10,5};

|

|

uint8_t index;

|

|

if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

|

|

{

|

|

*dl = dl_60Hz[index];

|

|

return bTRUE;

|

|

}

|

|

}

|

|

else if(pFilterInfo->ADCRate == ADCRATE_1P6MHZ && pFilterInfo->ADCSinc3Osr == ADCSINC3OSR_2)

|

|

{

|

|

//this combination suits for filter:

|

|

//SINC3 OSR2 for 1.6MSPS

|

|

const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_889, ADCSINC2OSR_1333};

|

|

const uint8_t dl_60Hz[] = {15,10};

|

|

uint8_t index;

|

|

if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

|

|

{

|

|

*dl = dl_60Hz[index];

|

|

return bTRUE;

|

|

}

|

|

}

|

|

else if(pFilterInfo->ADCRate == ADCRATE_800KHZ && pFilterInfo->ADCSinc3Osr != ADCSINC3OSR_2)

|

|

{

|

|

//this combination suits for filter:

|

|

//SINC3 OSR4 and OSR5 for 800kSPS,

|

|

const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_178, ADCSINC2OSR_267, ADCSINC2OSR_533, ADCSINC2OSR_667,\

|

|

ADCSINC2OSR_889, ADCSINC2OSR_1333};

|

|

const uint8_t dl_60Hz[] = {15,10,5,4,3,2};

|

|

uint8_t index;

|

|

if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

|

|

{

|

|

*dl = dl_60Hz[index];

|

|

return bTRUE;

|

|

}

|

|

}

|

|

*dl = 0;

|

|

return bFALSE;

|

|

}

|

|

|

|

/**

|

|

* @brief Calculate how many clocks are needed in sequencer wait command to generate required number of data from filter output.

|

|

* @note When measurement is done, it's recommend to disable blocks like ADCPWR, ADCCNV, SINC2, DFT etc. If blocks remain powered up,

|

|

* they may need less clocks to generate required number of output. Use function @ref AD5940_AFECtrlS to control these blocks.

|

|

* @param pFilterInfo: Pointer to configuration structure.

|

|

* @param pClocks: pointer used to store results.

|

|

* @return return none.

|

|

*/

|

|

void AD5940_ClksCalculate(ClksCalInfo_Type *pFilterInfo, uint32_t *pClocks)

|

|

{

|

|

uint32_t temp = 0;

|

|

const uint32_t sinc2osr_table[] = {22,44,89,178,267,533,640,667,800,889,1067,1333,0};

|

|

const uint32_t sinc3osr_table[] = {5,4,2,0};

|

|

|

|

*pClocks = 0;

|

|

if(pFilterInfo == NULL) return;

|

|

if(pClocks == NULL) return;

|

|

if(pFilterInfo->ADCSinc2Osr > ADCSINC2OSR_1333) return;

|

|

if(pFilterInfo->ADCSinc3Osr > 2) return; /* 0: OSR5, 1:OSR4, 2:OSR2 */

|

|

if(pFilterInfo->ADCAvgNum > ADCAVGNUM_16) return; /* Average number index:0,1,2,3 */

|

|

switch(pFilterInfo->DataType)

|

|

{

|

|

case DATATYPE_ADCRAW:

|

|

temp = (uint32_t)(20*pFilterInfo->DataCount*pFilterInfo->RatioSys2AdcClk);

|

|

break;

|

|

case DATATYPE_SINC3:

|

|

temp = (uint32_t)(((pFilterInfo->DataCount+2)*sinc3osr_table[pFilterInfo->ADCSinc3Osr]+1)*20*pFilterInfo->RatioSys2AdcClk + 0.5f);

|

|

break;

|

|

case DATATYPE_SINC2:

|

|

temp = (pFilterInfo->DataCount+1)*sinc2osr_table[pFilterInfo->ADCSinc2Osr] + 1;

|

|

pFilterInfo->DataType = DATATYPE_SINC3;

|

|

pFilterInfo->DataCount = temp;

|

|

AD5940_ClksCalculate(pFilterInfo, &temp);

|

|

pFilterInfo->DataType = DATATYPE_SINC2;

|

|

temp += 15; /* Need extra 15 clocks for FIFO etc. Just to be safe. */

|

|

break;

|

|

case DATATYPE_NOTCH:

|

|

{

|

|

ADCFilterCfg_Type filter;

|

|

filter.ADCRate = pFilterInfo->ADCRate;

|

|

filter.ADCSinc3Osr = pFilterInfo->ADCSinc3Osr;

|

|

filter.ADCSinc2Osr = pFilterInfo->ADCSinc2Osr;

|

|

uint8_t dl=0, dl_50, dl_60;

|

|

if(AD5940_Notch50HzAvailable(&filter, &dl_50)){

|

|

dl += dl_50 - 1;

|

|

}

|

|

if(AD5940_Notch60HzAvailable(&filter, &dl_60)){

|

|

dl += dl_60 - 1;

|

|

}

|

|

pFilterInfo->DataType = DATATYPE_SINC2;

|

|

pFilterInfo->DataCount += dl; //DL is the extra data input needed for filter to output first data.

|

|

AD5940_ClksCalculate(pFilterInfo,&temp);

|

|

//restore the filter info.

|

|

pFilterInfo->DataType = DATATYPE_NOTCH;

|

|

pFilterInfo->DataCount -= dl;

|

|

break;

|

|

}

|

|

case DATATYPE_DFT:

|

|

switch(pFilterInfo->DftSrc)

|

|

{

|

|

case DFTSRC_ADCRAW:

|

|

pFilterInfo->DataType = DATATYPE_ADCRAW;

|

|

AD5940_ClksCalculate(pFilterInfo, &temp);

|

|

break;

|

|

case DFTSRC_SINC3:

|

|

pFilterInfo->DataType = DATATYPE_SINC3;

|

|

AD5940_ClksCalculate(pFilterInfo, &temp);

|

|

break;

|

|

case DFTSRC_SINC2NOTCH:

|

|

if(pFilterInfo->BpNotch)

|

|

pFilterInfo->DataType = DATATYPE_SINC2;

|

|

else

|

|

pFilterInfo->DataType = DATATYPE_NOTCH;

|

|

AD5940_ClksCalculate(pFilterInfo, &temp);

|

|

break;

|

|

case DFTSRC_AVG:

|

|

pFilterInfo->DataType = DATATYPE_SINC3;

|

|

pFilterInfo->DataCount *= 1L<<(pFilterInfo->ADCAvgNum+1); /* 0: average2, 1: average4, 2: average8, 3: average16 */

|

|

AD5940_ClksCalculate(pFilterInfo, &temp);

|

|

break;

|

|

default:

|

|

break;

|

|

}

|

|

pFilterInfo->DataType = DATATYPE_DFT;

|

|

temp += 25; /* add margin */

|

|

break;

|

|

default:

|

|

break;

|

|

}

|

|

*pClocks = temp;

|

|

}

|

|

|

|

/**

|

|

@brief void AD5940_SweepNext(SoftSweepCfg_Type *pSweepCfg, float *pNextFreq)

|

|

For sweep function, calculate next frequency point according to pSweepCfg info.

|

|

@return Return next frequency point in Hz.

|

|

*/

|

|

void AD5940_SweepNext(SoftSweepCfg_Type *pSweepCfg, float *pNextFreq)

|

|

{

|

|

float frequency;

|

|

|

|

if(pSweepCfg->SweepLog)/* Log step */

|

|

{

|

|

if(pSweepCfg->SweepStart<pSweepCfg->SweepStop) /* Normal */

|

|

{

|

|

if(++pSweepCfg->SweepIndex == pSweepCfg->SweepPoints)

|

|

pSweepCfg->SweepIndex = 0;

|

|

frequency = pSweepCfg->SweepStart*pow(10,pSweepCfg->SweepIndex*log10(pSweepCfg->SweepStop/pSweepCfg->SweepStart)/(pSweepCfg->SweepPoints-1));

|

|

}

|

|

else

|

|

{

|

|

pSweepCfg->SweepIndex --;

|

|

if(pSweepCfg->SweepIndex >= pSweepCfg->SweepPoints)

|

|

pSweepCfg->SweepIndex = pSweepCfg->SweepPoints-1;

|

|

frequency = pSweepCfg->SweepStop*pow(10,pSweepCfg->SweepIndex*

|

|

(log10(pSweepCfg->SweepStart/pSweepCfg->SweepStop)/(pSweepCfg->SweepPoints-1)));

|

|

}

|

|

}

|

|

else/* Linear step */

|

|

{

|

|

if(pSweepCfg->SweepStart<pSweepCfg->SweepStop) /* Normal */

|

|

{

|

|

if(++pSweepCfg->SweepIndex == pSweepCfg->SweepPoints)

|

|

pSweepCfg->SweepIndex = 0;

|

|

frequency = pSweepCfg->SweepStart + pSweepCfg->SweepIndex*(double)(pSweepCfg->SweepStop-pSweepCfg->SweepStart)/(pSweepCfg->SweepPoints-1);

|

|

}

|

|

else

|

|

{

|

|

pSweepCfg->SweepIndex --;

|

|

if(pSweepCfg->SweepIndex >= pSweepCfg->SweepPoints)

|

|

pSweepCfg->SweepIndex = pSweepCfg->SweepPoints-1;

|

|

frequency = pSweepCfg->SweepStop + pSweepCfg->SweepIndex*(double)(pSweepCfg->SweepStart - pSweepCfg->SweepStop)/(pSweepCfg->SweepPoints-1);

|

|

}

|

|

}

|

|

|

|

*pNextFreq = frequency;

|

|

}

|

|

|

|

/**

|

|

@brief Initialize Structure members to zero

|

|

@param pStruct: Pointer to the structure.

|

|

@param StructSize: The structure size in Byte.

|

|

@return Return None.

|

|

**/

|

|

void AD5940_StructInit(void *pStruct, uint32_t StructSize)

|

|

{

|

|

memset(pStruct, 0, StructSize);

|

|

}

|

|

|

|

/**

|

|

@brief Convert ADC Code to voltage.

|

|

@param ADCPga: The ADC PGA used for this result.

|

|

@param code: ADC code.

|

|

@param VRef1p82: the actual 1.82V reference voltage.

|

|

@return Voltage in volt.

|

|

**/

|

|

float AD5940_ADCCode2Volt(uint32_t code, uint32_t ADCPga, float VRef1p82)

|

|

{

|

|

float kFactor = 1.835/1.82;

|

|

float fVolt = 0.0;

|

|

float tmp = 0;

|

|

tmp = (int32_t)code - 32768;

|

|

switch(ADCPga)

|

|

{

|

|

case ADCPGA_1:

|

|

break;

|

|

case ADCPGA_1P5:

|

|

tmp /= 1.5f;

|

|

break;

|

|

case ADCPGA_2:

|

|

tmp /= 2.0f;

|

|

break;

|

|

case ADCPGA_4:

|

|

tmp /= 4.0f;

|

|

break;

|

|

case ADCPGA_9:

|

|

tmp /= 9.0f;

|

|

break;

|

|

default:break;

|

|

}

|

|

fVolt = tmp*VRef1p82/32768*kFactor;

|

|

return fVolt;

|

|

}

|

|

|

|

/**

|

|

* @brief Do complex number division.

|

|

* @param a: The dividend.

|

|

* @param b: The divisor.

|

|

* @return Return result.

|

|

**/

|

|

fImpCar_Type AD5940_ComplexDivFloat(fImpCar_Type *a, fImpCar_Type *b)

|

|

{

|

|

fImpCar_Type res;

|

|

float temp;

|

|

temp = b->Real*b->Real + b->Image*b->Image;

|

|

res.Real = a->Real*b->Real + a->Image*b->Image;

|

|

res.Real /= temp;

|

|

res.Image = a->Image*b->Real - a->Real*b->Image;

|

|

res.Image /= temp;

|

|

return res;

|

|

}

|

|

|

|

/**

|

|

* @brief Do complex number multiplication.

|

|

* @param a: The multiplicand.

|

|

* @param b: The multiplier .

|

|

* @return Return result.

|

|

**/

|

|

fImpCar_Type AD5940_ComplexMulFloat(fImpCar_Type *a, fImpCar_Type *b)

|

|

{

|

|

fImpCar_Type res;

|

|

|

|

res.Real = a->Real*b->Real - a->Image*b->Image;

|

|

res.Image = a->Image*b->Real + a->Real*b->Image;

|

|

|

|

return res;

|

|

}

|

|

/**

|

|

* @brief Do complex number addition.

|

|

* @param a: The addend.

|

|

* @param b: The addend .

|

|

* @return Return result.

|

|

**/

|

|

fImpCar_Type AD5940_ComplexAddFloat(fImpCar_Type *a, fImpCar_Type *b)

|

|

{

|

|

fImpCar_Type res;

|

|

|

|

res.Real = a->Real + b->Real;

|

|

res.Image = a->Image + b->Image;

|

|

|

|

return res;

|

|

}

|

|

|

|

/**

|

|

* @brief Do complex number subtraction.

|

|

* @param a: The minuend.

|

|

* @param b: The subtrahend .

|

|

* @return Return result.

|

|

**/

|

|

fImpCar_Type AD5940_ComplexSubFloat(fImpCar_Type *a, fImpCar_Type *b)

|

|

{

|

|

fImpCar_Type res;

|

|

|

|

res.Real = a->Real - b->Real;

|

|

res.Image = a->Image - b->Image;

|

|

|

|

return res;

|

|

}

|

|

|

|

/**

|

|

* @brief Do complex number division.

|

|

* @param a: The dividend.

|

|

* @param b: The divisor.

|

|

* @return Return result.

|

|

**/

|

|

fImpCar_Type AD5940_ComplexDivInt(iImpCar_Type *a, iImpCar_Type *b)

|

|

{

|

|

fImpCar_Type res;

|

|

float temp;

|

|

temp = (float)b->Real*b->Real + (float)b->Image*b->Image;

|

|

res.Real = (float)a->Real*b->Real + (float)a->Image*b->Image;

|

|

res.Real /= temp;

|

|

res.Image = (float)a->Image*b->Real - (float)a->Real*b->Image;

|

|

res.Image /= temp;

|

|

return res;

|

|

}

|

|

|

|

/**

|

|

* @brief Do complex number multiplication.

|

|

* @param a: The multiplicand.

|

|

* @param b: The multiplier .

|

|

* @return Return result.

|

|

**/

|

|

fImpCar_Type AD5940_ComplexMulInt(iImpCar_Type *a, iImpCar_Type *b)

|

|

{

|

|

fImpCar_Type res;

|

|

|

|

res.Real = (float)a->Real*b->Real - (float)a->Image*b->Image;

|

|

res.Image = (float)a->Image*b->Real + (float)a->Real*b->Image;

|

|

|

|

return res;

|

|

}

|

|

|

|

/**

|

|

* @brief Calculate the complex number magnitude.

|

|

* @param a: The complex number.

|

|

* @return Return magnitude.

|

|

**/

|

|

float AD5940_ComplexMag(fImpCar_Type *a)

|

|

{

|

|

return sqrt(a->Real*a->Real + a->Image*a->Image);

|

|

}

|

|

|

|

/**

|

|

* @brief Calculate the complex number phase.

|

|

* @param a: The complex number.

|

|

* @return Return phase.

|

|

**/

|

|

float AD5940_ComplexPhase(fImpCar_Type *a)

|

|

{

|

|

return atan2(a->Image, a->Real);

|

|

}

|

|

|

|

/**

|

|

* @brief Calculate the optimum filter settings based on signal frequency.

|

|

* @param freq: Frequency of signalr.

|

|

* @return Return FreqParams.

|

|

**/

|

|

FreqParams_Type AD5940_GetFreqParameters(float freq)

|

|

{

|

|

const uint32_t dft_table[] = {4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096, 8192, 16384};

|

|

const uint32_t sinc2osr_table[] = {1, 22,44,89,178,267,533,640,667,800,889,1067,1333};

|

|

const uint32_t sinc3osr_table[] = {2, 4, 5};

|

|

float AdcRate = 800000;

|

|

uint32_t n1 = 0; // Sample rate after ADC filters

|

|

uint32_t n2 = 0; // Sample rate after DFT block

|

|

uint32_t iCycle = 0;

|

|

FreqParams_Type freq_params;

|

|

/* High power mode */

|

|

if(freq >= 20000)

|

|

{

|

|

freq_params. DftSrc = DFTSRC_SINC3;

|

|

freq_params.ADCSinc2Osr = 0;

|

|

freq_params.ADCSinc3Osr = 2;

|

|

freq_params.DftNum = DFTNUM_8192;

|

|

freq_params.NumClks = 0;

|

|

freq_params.HighPwrMode = bTRUE;

|

|

return freq_params;

|

|

}

|

|

|

|

if(freq < 0.51)

|

|

{

|

|

freq_params. DftSrc = DFTSRC_SINC2NOTCH;

|

|

freq_params.ADCSinc2Osr = 6;

|

|

freq_params.ADCSinc3Osr = 1;

|

|

freq_params.DftNum = DFTNUM_8192;

|

|

freq_params.NumClks = 0;

|

|

freq_params.HighPwrMode = bTRUE;

|

|

return freq_params;

|

|

}

|

|

|

|

/* Start with SINC2 setting */

|

|

for(uint8_t i = 0; i<sizeof(sinc2osr_table) / sizeof(uint32_t); i++)

|

|

{

|

|

n1 = sinc2osr_table[i] * sinc3osr_table[1];

|

|

if(((AdcRate/n1) < freq * 10) && (freq<20e3))

|

|

continue;

|

|

|

|

/* Try DFT number */

|

|

for(uint32_t j = 8; j<sizeof(dft_table) / sizeof(uint32_t); j++)

|

|

{

|

|

n2 = dft_table[j];

|

|

iCycle = (uint32_t)(n1 * n2 * freq)/AdcRate;

|

|

if(iCycle < 8)

|

|

continue;

|

|

freq_params. DftSrc = DFTSRC_SINC2NOTCH;

|

|

freq_params.ADCSinc2Osr = i-1;

|

|

freq_params.ADCSinc3Osr = 1;

|

|

freq_params.DftNum = j;

|

|

freq_params.NumClks = 0;

|

|

freq_params.HighPwrMode = bFALSE;

|

|

if(n1 == 4)

|

|

{

|

|

freq_params. DftSrc = DFTSRC_SINC3;

|

|

freq_params.ADCSinc2Osr = 0;

|

|

}

|

|

return freq_params;

|

|

}

|

|

}

|

|

|

|

return freq_params;

|

|

}

|

|

|

|

/**

|

|

* @} Function_Helpers

|

|

*/

|

|

|

|

#ifdef CHIPSEL_M355

|

|

static void AD5940_D2DWriteReg(uint16_t RegAddr, uint32_t RegData)

|

|

{

|

|

if(((RegAddr>=0x1000)&&(RegAddr<=0x3014))) /* 32bit register */

|

|

*(volatile uint32_t *)(RegAddr+0x400c0000) = RegData;

|

|

else /* 16bit register */

|

|

*(volatile uint16_t *)(RegAddr+0x400c0000) = RegData;

|

|

}

|

|

|

|

static uint32_t AD5940_D2DReadReg(uint16_t RegAddr)

|

|

{

|

|

if(((RegAddr>=0x1000)&&(RegAddr<=0x3014))) /* 32bit register */

|

|

return *(volatile uint32_t *)(RegAddr+0x400c0000);

|

|

else /* 16bit register */

|

|

return *(volatile uint16_t *)(RegAddr+0x400c0000);

|

|

}

|

|

|

|

void AD5940_FIFORd(uint32_t *pBuffer, uint32_t uiReadCount)

|

|

{

|

|

while(uiReadCount--)

|

|

*pBuffer++ = *(volatile uint32_t *)(0x400c206C);

|

|

}

|

|

#else

|

|

/**

|

|

* @defgroup SPI_Block

|

|

* @brief Functions to communicate with AD5940 registers following AD5940 SPI protocols

|

|

* @{

|

|

*

|

|

* @defgroup SPI_Block_Functions

|

|

* @brief The basic SPI protocols. All functions are basic on AD5940_ReadWriteNBytes which

|

|

* provided by user.

|

|

*

|

|

* ##SPI basic protocol

|

|

* All SPI protocol starts with one-byte command word. Following are data(16B or 32B)

|

|

* There are four SPI commands available @ref SPI_Block_Const.

|

|

* @{

|

|

*/

|

|

|

|

/**

|

|

@brief Using SPI to transmit one byte and return the received byte.

|

|

@param data: The 8-bit data SPI will transmit.

|

|

@return received data.

|

|

**/

|

|

static unsigned char AD5940_ReadWrite8B(unsigned char data)

|

|

{

|

|

uint8_t tx[1], rx[1];

|

|

tx[0] = data;

|

|

AD5940_ReadWriteNBytes(tx,rx,1);

|

|

return rx[0];

|

|

}

|

|

|

|

/**

|

|

@brief Using SPI to transmit two bytes and return the received bytes.

|

|

@param data: The 16-bit data SPI will transmit.

|

|

@return received data.

|

|

**/

|

|

static uint16_t AD5940_ReadWrite16B(uint16_t data)

|

|

{

|

|

uint8_t SendBuffer[2];

|

|

uint8_t RecvBuffer[2];

|

|

SendBuffer[0] = data>>8;

|

|

SendBuffer[1] = data&0xff;

|

|

AD5940_ReadWriteNBytes(SendBuffer,RecvBuffer,2);

|

|

return (((uint16_t)RecvBuffer[0])<<8)|RecvBuffer[1];

|

|

}

|

|

|

|

/**

|

|

* @brief Using SPI to transmit four bytes and return the received bytes.

|

|

* @param data: The 32-bit data SPI will transmit.

|

|

* @return received data.

|

|

**/

|

|

static uint32_t AD5940_ReadWrite32B(uint32_t data)

|

|

{

|

|

uint8_t SendBuffer[4];

|

|

uint8_t RecvBuffer[4];

|

|

|

|

SendBuffer[0] = (data>>24)&0xff;

|

|

SendBuffer[1] = (data>>16)&0xff;

|

|

SendBuffer[2] = (data>> 8)&0xff;

|

|

SendBuffer[3] = (data )&0xff;

|

|

AD5940_ReadWriteNBytes(SendBuffer,RecvBuffer,4);

|

|

return (((uint32_t)RecvBuffer[0])<<24)|(((uint32_t)RecvBuffer[1])<<16)|(((uint32_t)RecvBuffer[2])<<8)|RecvBuffer[3];

|

|

}

|

|

|

|

/**

|

|

* @brief Write register through SPI.

|

|

* @param RegAddr: The register address.

|

|

* @param RegData: The register data.

|

|

* @return Return None.

|

|

**/

|

|

static void AD5940_SPIWriteReg(uint16_t RegAddr, uint32_t RegData)

|

|

{

|

|

/* Set register address */

|

|

AD5940_CsClr();

|

|

AD5940_ReadWrite8B(SPICMD_SETADDR);

|

|

AD5940_ReadWrite16B(RegAddr);

|

|

AD5940_CsSet();

|

|

/* Add delay here to meet the SPI timing. */

|

|

AD5940_CsClr();

|

|

AD5940_ReadWrite8B(SPICMD_WRITEREG);

|

|

if(((RegAddr>=0x1000)&&(RegAddr<=0x3014)))

|

|

AD5940_ReadWrite32B(RegData);

|

|

else

|

|

AD5940_ReadWrite16B(RegData);

|

|

AD5940_CsSet();

|

|

}

|

|

|

|

/**

|

|

* @brief Read register through SPI.

|

|

* @param RegAddr: The register address.

|

|

* @return Return register data.

|

|

**/

|

|

static uint32_t AD5940_SPIReadReg(uint16_t RegAddr)

|

|

{

|

|

uint32_t Data = 0;

|

|

/* Set register address that we want to read */

|

|

AD5940_CsClr();

|

|

AD5940_ReadWrite8B(SPICMD_SETADDR);

|

|

AD5940_ReadWrite16B(RegAddr);

|

|

AD5940_CsSet();

|

|

/* Read it */

|

|

AD5940_CsClr();

|

|

AD5940_ReadWrite8B(SPICMD_READREG);

|

|

AD5940_ReadWrite8B(0); //Dummy read

|

|

/* The real data is coming */

|

|

if((RegAddr>=0x1000)&&(RegAddr<=0x3014))

|

|

Data = AD5940_ReadWrite32B(0);

|

|

else

|

|

Data = AD5940_ReadWrite16B(0);

|

|

AD5940_CsSet();

|

|

return Data;

|

|

}

|

|

|

|

/**

|

|

@brief Read specific number of data from FIFO with optimized SPI access.

|

|

@param pBuffer: Pointer to a buffer that used to store data read back.

|

|

@param uiReadCount: How much data to be read.

|

|

@return none.

|

|

**/

|

|

void AD5940_FIFORd(uint32_t *pBuffer, uint32_t uiReadCount)

|

|

{

|

|

/* Use function AD5940_SPIReadReg to read REG_AFE_DATAFIFORD is also one method. */

|

|

uint32_t i;

|

|

|

|

if(uiReadCount < 3)

|

|

{

|

|

/* This method is more efficient when readcount < 3 */

|

|

uint32_t i;

|

|

AD5940_CsClr();

|

|

AD5940_ReadWrite8B(SPICMD_SETADDR);

|

|

AD5940_ReadWrite16B(REG_AFE_DATAFIFORD);

|

|

AD5940_CsSet();

|

|

for(i=0;i<uiReadCount;i++)

|

|

{

|

|

AD5940_CsClr();

|

|

AD5940_ReadWrite8B(SPICMD_READREG);

|

|

AD5940_ReadWrite8B(0);//Write Host status/Don't care

|

|

pBuffer[i] = AD5940_ReadWrite32B(0);

|

|

AD5940_CsSet();

|

|

}

|

|

}

|

|

else

|

|

{

|

|

AD5940_CsClr();

|

|

AD5940_ReadWrite8B(SPICMD_READFIFO);

|

|

/* 6 dummy write before valid data read back */

|

|

for(i=0;i<6;i++)

|

|

AD5940_ReadWrite8B(0);

|

|

/* Continuously read DATAFIFORD register with offset 0 */

|

|

for(i=0;i<uiReadCount-2;i++)

|

|

{

|

|

pBuffer[i] = AD5940_ReadWrite32B(0); /*Offset is 0, so we always read DATAFIFORD register */

|

|

}

|

|

/* Read back last two FIFO data with none-zero offset*/

|

|

pBuffer[i++] = AD5940_ReadWrite32B(0x44444444);

|

|

pBuffer[i] = AD5940_ReadWrite32B(0x44444444);

|

|

AD5940_CsSet();

|

|

}

|

|

}

|

|

|

|

/**

|

|

* @} SPI_Block_Functions

|

|

* @} SPI_Block

|

|

*/

|

|

#endif

|

|

|

|

/**

|

|

* @brief Write register. If sequencer generator is enabled, the register write is recorded.

|

|

* Otherwise, the data is written to AD5940 by SPI.

|

|

* @param RegAddr: The register address.

|

|

* @param RegData: The register data.

|

|

* @return Return None.

|

|

**/

|

|

void AD5940_WriteReg(uint16_t RegAddr, uint32_t RegData)

|

|

{

|

|

#ifdef SEQUENCE_GENERATOR

|

|

if(SeqGenDB.EngineStart == bTRUE)

|

|

AD5940_SEQWriteReg(RegAddr, RegData);

|

|

else

|

|

#endif

|

|

#ifdef CHIPSEL_M355

|

|

AD5940_D2DWriteReg(RegAddr, RegData);

|

|

#else

|

|

AD5940_SPIWriteReg(RegAddr, RegData);

|

|

#endif

|

|

}

|

|

|

|

/**

|

|

* @brief Read register. If sequencer generator is enabled, read current register value from data-base.

|

|

* Otherwise, read register value by SPI.

|

|

* @param RegAddr: The register address.

|

|

* @return Return register value.

|

|

**/

|

|

uint32_t AD5940_ReadReg(uint16_t RegAddr)

|

|

{

|

|

#ifdef SEQUENCE_GENERATOR

|

|

if(SeqGenDB.EngineStart == bTRUE)

|

|

return AD5940_SEQReadReg(RegAddr);

|

|

else

|

|

#endif

|

|

#ifdef CHIPSEL_M355

|

|

return AD5940_D2DReadReg(RegAddr);

|

|

#else

|

|

return AD5940_SPIReadReg(RegAddr);

|

|

#endif

|

|

}

|

|

|

|

|

|

/**

|

|

* @defgroup AFE_Control

|

|

* @brief Some functions to control the whole AFE. They are top level switches.

|

|

* @{

|

|

* @defgroup AFE_Control_Functions

|

|

* The top-level control functions for whole AFE perspective.

|

|

* @details This function set is used to control the whole AFE block by block. It's a top-level configuration.

|

|

* It's convenient when do initialization work with the functions called BLOCK**Cfg**. You can tune the parameters at run-time using more detailed

|

|

* functions from each block. rather than top-level functions where you need to configure all parameters.

|

|

* @{

|

|

*/

|

|

|

|

/**

|

|

* @brief Initialize AD5940. This function must be called whenever there is reset(Software Reset or Hardware reset or Power up) happened.

|

|

* This function is used to put AD5940 to correct state.

|

|

* @return return None

|

|

**/

|

|

void AD5940_Initialize(void)

|

|

{

|

|

int i;

|

|

/* Write following registers with its data sequentially whenever there is a reset happened. */

|

|

const struct

|

|

{

|

|

uint16_t reg_addr;

|

|

uint32_t reg_data;

|

|

}RegTable[]=

|

|

{

|

|

{0x0908, 0x02c9},

|

|

{0x0c08, 0x206C},

|

|

{0x21F0, 0x0010},

|

|

#ifndef CHIPSEL_M355

|

|

/* This is AD5940 */

|

|

{0x0410, 0x02c9},

|

|

{0x0A28, 0x0009},

|

|

#else

|

|

/* This is ADuCM355 */

|

|

{0x0410, 0x001a},

|

|

{0x0A28, 0x0008},

|

|

#endif

|

|

{0x238c, 0x0104},

|

|

{0x0a04, 0x4859},

|

|

{0x0a04, 0xF27B},

|

|

{0x0a00, 0x8009},

|

|

{0x22F0, 0x0000},

|

|

//

|

|

{0x2230, 0xDE87A5AF},

|

|

{0x2250, 0x103F},

|

|

{0x22B0, 0x203C},

|

|

{0x2230, 0xDE87A5A0},

|

|

};

|

|

//initialize global variables

|

|

SeqGenDB.SeqLen = 0;

|

|

SeqGenDB.RegCount = 0;

|

|

SeqGenDB.LastError = AD5940ERR_OK;

|

|

SeqGenDB.EngineStart = bFALSE;

|

|

#ifndef CHIPSEL_M355

|

|

AD5940_CsSet(); /* Pull high CS in case it's low */

|

|

#endif

|

|

for(i=0; i<sizeof(RegTable)/sizeof(RegTable[0]); i++)

|

|

AD5940_WriteReg(RegTable[i].reg_addr, RegTable[i].reg_data);

|

|

i = AD5940_ReadReg(REG_AFECON_CHIPID);

|

|

if(i == 0x5501)

|

|

bIsS2silicon = bTRUE;

|

|

else if(i == 0x5502) /* S3 chip-id is 0x5502. The is no difference with S2. */

|

|

bIsS2silicon = bTRUE;

|

|

else if(i == 0x5500)

|

|

bIsS2silicon = bFALSE;

|

|

#ifdef ADI_DEBUG

|

|

else

|

|

{

|

|

printf("CHIPID read error:0x%04x. AD5940 is not present?\n", i);

|

|

while(1);

|

|

}

|

|

#ifdef CHIPSEL_M355

|

|

ADI_Print("This ADuCM355!\n");

|

|

#else

|

|

ADI_Print("This AD594x!\n");

|

|

#endif

|

|

ADI_Print("Note: Current Silicon is %s\n", bIsS2silicon?"S2":"S1");

|

|

ADI_Print("AD5940LIB Version:v%d.%d.%d\n", AD5940LIB_VER_MAJOR, AD5940LIB_VER_MINOR, AD5940LIB_VER_PATCH);

|

|

#endif

|

|

}

|

|

|

|

/**

|

|

* @brief Control most AFE digital and analog block within one register access.

|

|

* @param AfeCtrlSet: A set of blocks that will be controlled select it from @ref AFECTRL_Const Below is two examples to use it.

|

|

* - AFECTRL_HPREFPWR: Control high power reference(bandgap).

|

|

* - AFECTRL_WG|AFECTRL_ADCPWR: The OR'ed control set. Control Waveform generator and ADC power.

|

|

* @param State: Enable or disable selected control set signal. Select from @BoolFlag

|

|

* - bFALSE: Disable or power down selected block(s).

|

|

* - bTRUE: Enable all selected block(s).

|

|

@return return none.

|

|

*/

|

|

void AD5940_AFECtrlS(uint32_t AfeCtrlSet, BoolFlag State)

|

|

{

|

|

/* Check parameters */

|

|

uint32_t tempreg;

|

|

tempreg = AD5940_ReadReg(REG_AFE_AFECON);

|

|

if (State == bTRUE) {

|

|

/* Clear bits to enable HPREF and ALDOLimit*/

|

|

if (AfeCtrlSet & AFECTRL_HPREFPWR) {

|

|

tempreg &= ~BITM_AFE_AFECON_HPREFDIS;

|

|

AfeCtrlSet &= ~AFECTRL_HPREFPWR;

|

|

}

|

|

if(AfeCtrlSet & AFECTRL_ALDOLIMIT)

|

|

{

|

|

tempreg &= ~BITM_AFE_AFECON_ALDOILIMITEN;

|

|

AfeCtrlSet &= ~AFECTRL_ALDOLIMIT;

|

|

}

|

|

tempreg |= AfeCtrlSet;

|

|

}

|

|

else

|

|

{

|

|

/* Set bits to Disable HPREF and ALDOLimit*/

|

|

if(AfeCtrlSet & AFECTRL_HPREFPWR)

|

|

{

|

|

tempreg |= BITM_AFE_AFECON_HPREFDIS;

|

|

AfeCtrlSet &= ~AFECTRL_HPREFPWR;

|

|

}

|

|

if(AfeCtrlSet & AFECTRL_ALDOLIMIT)

|

|

{

|

|

tempreg |= BITM_AFE_AFECON_ALDOILIMITEN;

|

|

AfeCtrlSet &= ~AFECTRL_ALDOLIMIT;

|

|

}

|

|

tempreg &= ~AfeCtrlSet;

|

|

}

|

|

AD5940_WriteReg(REG_AFE_AFECON, tempreg);

|

|

}

|

|

/** When LP mode is enabled, some functions are under control of LPMODECON, rather than original registers. */

|

|

/** @warning LPMODE is key protected, this function only takes effect after AD5940_LPModeEnS(bTRUE) */

|

|

/**

|

|

* @brief For LP mode, use one register to control most AFE digital and analog block.

|

|

* @details The parameter means the blocks. The selected block will be enabled. All others will be disabled.

|

|

* The method to enable/disable blocks are defined by register LPMODECON, either by clearing or setting bits.

|

|

* @param EnSet: A set of blocks that will be enabled. Select it from @ref LPMODECTRL_Const. All others not selected in EnSet will be disabled.

|

|

* - LPMODECTRL_ALDOPWR|LPMODECTRL_HFOSCEN: Turn on ALDO and HFOSC, disable all others.

|

|

* - LPMODECTRL_ALL: Enable all blocks.

|

|

@return return none.

|

|

*/

|

|

AD5940Err AD5940_LPModeCtrlS(uint32_t EnSet)

|

|

{

|

|

/* Check parameters */

|

|

uint32_t tempreg;

|

|

uint32_t DisSet; /* The blocks to be disabled */

|

|

DisSet = LPMODECTRL_ALL & (~EnSet);

|

|

tempreg = AD5940_ReadReg(REG_AFE_LPMODECON);

|

|

/* Enable selected set */

|

|

{

|

|

/* Clear bits to enable HFOSC, HPREF, ALDO */

|

|

if (EnSet & LPMODECTRL_HFOSCEN) {

|

|

tempreg &= ~BITM_AFE_LPMODECON_HFOSCPD;

|

|

EnSet &= ~LPMODECTRL_HFOSCEN;

|

|

}

|

|

if(EnSet & LPMODECTRL_HPREFPWR)

|

|

{

|

|

tempreg &= ~BITM_AFE_LPMODECON_HPREFDIS;

|

|

EnSet &= ~LPMODECTRL_HPREFPWR;

|

|

}

|

|

if(EnSet & LPMODECTRL_ALDOPWR)

|

|

{

|

|

tempreg &= ~BITM_AFE_LPMODECON_ALDOEN;

|

|

EnSet &= ~LPMODECTRL_ALDOPWR;

|

|

}

|

|

tempreg |= EnSet; /* Set other bits to enable function */

|

|

}

|

|

/* Disable other blocks */

|

|

{

|

|

/* Set bits to disable HFOSC, HPREF, ALDO */

|

|

if (DisSet & LPMODECTRL_HFOSCEN) {

|

|

tempreg |= BITM_AFE_LPMODECON_HFOSCPD;

|

|

DisSet &= ~LPMODECTRL_HFOSCEN;

|

|

}

|

|

if(DisSet & LPMODECTRL_HPREFPWR)

|

|

{

|

|

tempreg |= BITM_AFE_LPMODECON_HPREFDIS;

|

|

DisSet &= ~LPMODECTRL_HPREFPWR;

|

|

}

|

|

if(DisSet & LPMODECTRL_ALDOPWR)

|

|

{

|

|

tempreg |= BITM_AFE_LPMODECON_ALDOEN;

|

|

DisSet &= ~LPMODECTRL_ALDOPWR;

|

|

}

|

|

tempreg &= ~DisSet; /* Clear other bits to disable function */

|

|

}

|

|

AD5940_WriteReg(REG_AFE_LPMODECON, tempreg);

|

|

|

|

return AD5940ERR_OK;

|

|

}

|

|

|

|

/**

|

|

@brief Set AFE power mode and system bandwidth include HSDAC, Excitation-buffer, HSTIA and ADC etc.

|

|

@param AfePwr : {AFEPWR_LP, AFEPWR_HP}

|

|

Select parameters from @ref AFEPWR_Const

|

|

- AFEPWR_LP: Set AFE to low power mode

|

|

- AFEPWR_HP: Set AFE to High speed mode to support 200kHz.

|

|

@param AfeBw : {AFEBW_AUTOSET, AFEBW_50KHZ, AFEBW_100KHZ, AFEBW_250KHZ}

|

|

- AFEBW_AUTOSET: Set the bandwidth automatically based on WGFCW frequency word.

|

|

- AFEBW_50KHZ: Set system bandwidth to 50kHz.

|

|

- AFEBW_100KHZ: Set system bandwidth to 100kHz.

|

|

- AFEBW_250KHZ: Set system bandwidth to 250kHz.

|

|

@return return none.

|

|

*/

|

|

void AD5940_AFEPwrBW(uint32_t AfePwr, uint32_t AfeBw)

|

|

{

|

|

//check parameters

|

|

uint32_t tempreg;

|

|

tempreg = AfePwr;

|

|

tempreg |= AfeBw << BITP_AFE_PMBW_SYSBW;

|

|

AD5940_WriteReg(REG_AFE_PMBW, tempreg);

|

|

}

|

|

|

|

/**

|

|

@brief Configure reference buffer include 1.8V/1.1V high/low power buffers.

|

|

@param pBufCfg :Pointer to buffer configure structure;

|

|

@return return none.

|

|

*/

|

|

void AD5940_REFCfgS(AFERefCfg_Type *pBufCfg)

|

|

{

|

|

uint32_t tempreg;

|

|

|

|

/* HP Reference(bandgap) */

|

|

tempreg = AD5940_ReadReg(REG_AFE_AFECON);

|

|

tempreg &= ~BITM_AFE_AFECON_HPREFDIS;

|

|

if(pBufCfg->HpBandgapEn == bFALSE)

|

|

tempreg |= BITM_AFE_AFECON_HPREFDIS;

|

|

AD5940_WriteReg(REG_AFE_AFECON, tempreg);

|

|

/* Reference buffer configure */

|

|

tempreg = AD5940_ReadReg(REG_AFE_BUFSENCON);

|

|

if(pBufCfg->Hp1V8BuffEn == bTRUE)

|

|

tempreg |= BITM_AFE_BUFSENCON_V1P8HPADCEN;

|

|

if(pBufCfg->Hp1V1BuffEn == bTRUE)

|

|

tempreg |= BITM_AFE_BUFSENCON_V1P1HPADCEN;

|

|

if(pBufCfg->Lp1V8BuffEn == bTRUE)

|

|

tempreg |= BITM_AFE_BUFSENCON_V1P8LPADCEN;

|

|

if(pBufCfg->Lp1V1BuffEn == bTRUE)

|

|

tempreg |= BITM_AFE_BUFSENCON_V1P1LPADCEN;

|

|

if(pBufCfg->Hp1V8ThemBuff == bTRUE)

|

|

tempreg |= BITM_AFE_BUFSENCON_V1P8THERMSTEN;

|

|

if(pBufCfg->Hp1V8Ilimit == bTRUE)

|

|

tempreg |= BITM_AFE_BUFSENCON_V1P8HPADCILIMITEN;

|

|

if(pBufCfg->Disc1V8Cap == bTRUE)

|

|

tempreg |= BITM_AFE_BUFSENCON_V1P8HPADCCHGDIS;

|

|

if(pBufCfg->Disc1V1Cap == bTRUE)

|

|

tempreg |= BITM_AFE_BUFSENCON_V1P1LPADCCHGDIS;

|

|

AD5940_WriteReg(REG_AFE_BUFSENCON, tempreg);

|

|

|

|

/* LPREFBUFCON */

|

|

tempreg = 0;

|

|

if(pBufCfg->LpRefBufEn == bFALSE)

|

|

tempreg |= BITM_AFE_LPREFBUFCON_LPBUF2P5DIS;

|

|

if(pBufCfg->LpBandgapEn == bFALSE)

|

|

tempreg |= BITM_AFE_LPREFBUFCON_LPREFDIS;

|

|

if(pBufCfg->LpRefBoostEn == bTRUE)

|

|

tempreg |= BITM_AFE_LPREFBUFCON_BOOSTCURRENT;

|

|

AD5940_WriteReg(REG_AFE_LPREFBUFCON, tempreg);

|

|

}

|

|

/**

|

|

* @} End of AFE_Control_Functions

|

|

* @} End of AFE_Control

|

|

* */

|

|

|

|

/**

|

|

* @defgroup High_Speed_Loop

|

|

* @brief The high speed loop

|

|

* @{

|

|

* @defgroup High_Speed_Loop_Functions

|

|

* @{

|

|

*/

|

|

|

|

/**

|

|

@brief Configure High speed loop(high bandwidth loop or

|

|

called excitation loop). This configuration includes HSDAC, HSTIA and Switch matrix.

|

|

@param pHsLoopCfg : Pointer to configure structure;

|

|

@return return none.

|

|

*/

|

|

void AD5940_HSLoopCfgS(HSLoopCfg_Type *pHsLoopCfg)

|

|

{

|

|

AD5940_HSDacCfgS(&pHsLoopCfg->HsDacCfg);

|

|

AD5940_HSTIACfgS(&pHsLoopCfg->HsTiaCfg);

|

|

AD5940_SWMatrixCfgS(&pHsLoopCfg->SWMatCfg);

|

|

AD5940_WGCfgS(&pHsLoopCfg->WgCfg);

|

|

}

|

|

|

|

/**

|

|

@brief Initialize switch matrix

|

|

@param pSwMatrix: Pointer to configuration structure

|

|

@return return none.

|

|

*/

|

|

void AD5940_SWMatrixCfgS(SWMatrixCfg_Type *pSwMatrix)

|

|

{

|

|

AD5940_WriteReg(REG_AFE_DSWFULLCON, pSwMatrix->Dswitch);

|

|

AD5940_WriteReg(REG_AFE_PSWFULLCON, pSwMatrix->Pswitch);

|

|

AD5940_WriteReg(REG_AFE_NSWFULLCON, pSwMatrix->Nswitch);

|

|

AD5940_WriteReg(REG_AFE_TSWFULLCON, pSwMatrix->Tswitch);

|

|

AD5940_WriteReg(REG_AFE_SWCON, BITM_AFE_SWCON_SWSOURCESEL); /* Update switch configuration */

|

|

}

|

|

|

|

/**

|

|

@brief Initialize HSDAC

|

|

@param pHsDacCfg: Pointer to configuration structure

|

|

@return return none.

|

|

*/

|

|

void AD5940_HSDacCfgS(HSDACCfg_Type *pHsDacCfg)

|

|

{

|

|

uint32_t tempreg;

|

|

//Check parameters

|

|

tempreg = 0;

|

|

if(pHsDacCfg->ExcitBufGain == EXCITBUFGAIN_0P25)

|

|

tempreg |= BITM_AFE_HSDACCON_INAMPGNMDE; /* Enable attenuator */

|

|

if(pHsDacCfg->HsDacGain == HSDACGAIN_0P2)

|

|

tempreg |= BITM_AFE_HSDACCON_ATTENEN; /* Enable attenuator */

|

|

tempreg |= (pHsDacCfg->HsDacUpdateRate&0xff)<<BITP_AFE_HSDACCON_RATE;

|

|

AD5940_WriteReg(REG_AFE_HSDACCON, tempreg);

|

|

}

|

|

|

|

|

|

void __AD5940_SetDExRTIA(uint32_t DExPin, uint32_t DeRtia, uint32_t DeRload)

|

|

{

|

|

uint32_t tempreg;

|

|

/* deal with HSTIA DE RTIA */

|

|

if(DeRtia >= HSTIADERTIA_OPEN)

|

|

tempreg = 0x1f << 3; /* bit field HPTIRES03CON[7:3] */

|

|

else if(DeRtia >= HSTIADERTIA_1K)

|

|

{

|

|

tempreg = (DeRtia - 3 + 11) << 3;

|

|

}

|

|

else /* DERTIA 50/100/200Ohm */

|

|

{

|

|

const uint8_t DeRtiaTable[3][5] =

|

|

{

|

|

//Rload 0 10 30 50 100

|

|

{0x00, 0x01, 0x02, 0x03, 0x06}, /* RTIA 50Ohm */

|

|

{0x03, 0x04, 0x05, 0x06, 0x07}, /* RTIA 100Ohm */

|

|

{0x07, 0x07, 0x09, 0x09, 0x0a}, /* RTIA 200Ohm */

|

|

};

|

|

if(DeRload < HSTIADERLOAD_OPEN)

|

|

tempreg = (uint32_t)(DeRtiaTable[DeRtia][DeRload])<<3;

|

|

else

|

|

tempreg = (0x1f)<<3; /* Set it to HSTIADERTIA_OPEN. This setting is illegal */

|

|

}

|

|

/* deal with HSTIA Rload */

|

|

tempreg |= DeRload;

|

|

if(DExPin) //DE1

|

|

AD5940_WriteReg(REG_AFE_DE1RESCON, tempreg);

|

|

else //DE0

|

|

AD5940_WriteReg(REG_AFE_DE0RESCON, tempreg);

|

|

}

|

|

|

|

/**

|

|

@brief Initialize High speed TIA amplifier

|

|

@param pHsTiaCfg: Pointer to configuration structure

|

|

@return return none.

|

|

*/

|

|

AD5940Err AD5940_HSTIACfgS(HSTIACfg_Type *pHsTiaCfg)

|

|

{

|

|

uint32_t tempreg;

|

|

//Check parameters

|

|

if(pHsTiaCfg == NULL) return AD5940ERR_NULLP;

|

|

/* Available parameter is 1k, 5k,...,160k, short, OPEN */

|

|

if(pHsTiaCfg->HstiaDeRtia < HSTIADERTIA_1K)

|

|

return AD5940ERR_PARA;

|

|

if(pHsTiaCfg->HstiaDeRtia > HSTIADERTIA_OPEN)

|

|

return AD5940ERR_PARA; /* Parameter is invalid */

|

|

|

|

if(pHsTiaCfg->HstiaDeRload > HSTIADERLOAD_OPEN)

|

|

return AD5940ERR_PARA; /* Available parameter is OPEN, 0R,..., 100R */

|

|

|

|

tempreg = 0;

|

|

tempreg |= pHsTiaCfg->HstiaBias;

|

|

AD5940_WriteReg(REG_AFE_HSTIACON, tempreg);

|

|

/* HSRTIACON */

|

|

/* Calculate CTIA value */

|

|

tempreg = pHsTiaCfg->HstiaCtia << BITP_AFE_HSRTIACON_CTIACON;

|

|

tempreg |= pHsTiaCfg->HstiaRtiaSel;

|

|

if(pHsTiaCfg->DiodeClose == bTRUE)

|

|

tempreg |= BITM_AFE_HSRTIACON_TIASW6CON; /* Close switch 6 */

|

|

AD5940_WriteReg(REG_AFE_HSRTIACON, tempreg);

|

|

/* DExRESCON */

|

|

__AD5940_SetDExRTIA(0, pHsTiaCfg->HstiaDeRtia, pHsTiaCfg->HstiaDeRload);

|

|

#ifdef CHIPSEL_M355

|

|

__AD5940_SetDExRTIA(1, pHsTiaCfg->HstiaDe1Rtia, pHsTiaCfg->HstiaDe1Rload);

|

|

#endif

|

|

|

|

/* Done */

|

|

return AD5940ERR_OK;

|

|

}

|

|

/**

|

|

* @brief Configure HSTIA RTIA resistor and keep other parameters unchanged.

|

|

* @param HSTIARtia: The RTIA setting, select it from @ref HSTIARTIA_Const

|

|

* @return return none.

|

|

*/

|

|

void AD5940_HSRTIACfgS(uint32_t HSTIARtia)

|

|

{

|

|

uint32_t tempreg;

|

|

tempreg = AD5940_ReadReg(REG_AFE_HSRTIACON);

|

|

tempreg &= ~BITM_AFE_HSRTIACON_RTIACON;

|

|

HSTIARtia &= BITM_AFE_HSRTIACON_RTIACON;

|

|

tempreg |= HSTIARtia<<BITP_AFE_HSRTIACON_RTIACON;

|

|

AD5940_WriteReg(REG_AFE_HSRTIACON, tempreg);

|

|

}

|

|

|

|

/**

|

|

* @defgroup Waveform_Generator_Functions

|

|

* @{

|

|

*/

|

|

/**

|

|

* @brief Initialize waveform generator

|

|

* @param pWGInit: Pointer to configuration structure

|

|

* @return return none.

|

|

*/

|

|

void AD5940_WGCfgS(WGCfg_Type *pWGInit)

|

|

{

|

|

//Check parameters

|

|

uint32_t tempreg;

|

|

if(pWGInit->WgType == WGTYPE_SIN)

|

|

{

|

|

/* Configure Sine wave Generator */

|

|

AD5940_WriteReg(REG_AFE_WGFCW, pWGInit->SinCfg.SinFreqWord);

|

|

AD5940_WriteReg(REG_AFE_WGAMPLITUDE, pWGInit->SinCfg.SinAmplitudeWord);

|

|

AD5940_WriteReg(REG_AFE_WGOFFSET, pWGInit->SinCfg.SinOffsetWord);

|

|

AD5940_WriteReg(REG_AFE_WGPHASE, pWGInit->SinCfg.SinPhaseWord);

|

|

}

|

|

else if(pWGInit->WgType == WGTYPE_TRAPZ)

|

|

{

|

|

/* Configure Trapezoid Generator */

|

|

AD5940_WriteReg(REG_AFE_WGDCLEVEL1, pWGInit->TrapzCfg.WGTrapzDCLevel1);

|

|

AD5940_WriteReg(REG_AFE_WGDCLEVEL2, pWGInit->TrapzCfg.WGTrapzDCLevel2);

|

|

AD5940_WriteReg(REG_AFE_WGDELAY1, pWGInit->TrapzCfg.WGTrapzDelay1);

|

|

AD5940_WriteReg(REG_AFE_WGDELAY2, pWGInit->TrapzCfg.WGTrapzDelay2);

|

|

AD5940_WriteReg(REG_AFE_WGSLOPE1, pWGInit->TrapzCfg.WGTrapzSlope1);

|

|

AD5940_WriteReg(REG_AFE_WGSLOPE2, pWGInit->TrapzCfg.WGTrapzSlope2);

|

|

}

|

|

else

|

|

{

|

|

/* Write DAC data. It's only have effect when WgType set to WGTYPE_MMR */

|

|

AD5940_WriteReg(REG_AFE_HSDACDAT, pWGInit->WgCode);

|

|

}

|

|

tempreg = 0;

|

|

|

|

if(pWGInit->GainCalEn == bTRUE)

|

|

tempreg |= BITM_AFE_WGCON_DACGAINCAL;

|

|

if(pWGInit->OffsetCalEn == bTRUE)

|

|

tempreg |= BITM_AFE_WGCON_DACOFFSETCAL;

|

|

tempreg |= (pWGInit->WgType) << BITP_AFE_WGCON_TYPESEL;

|

|