diff --git a/#AD5940.h reference.md b/#AD5940.h reference.md

new file mode 100644

index 0000000..e388ff8

--- /dev/null

+++ b/#AD5940.h reference.md

@@ -0,0 +1,811 @@

+# # AD594x AFE Controller: A Streamlined Register and Functional Reference

+--------------------------------------------------------------------------------

+### 1.0 Introduction

+This document serves as a streamlined, developer-focused technical reference for the Analog Devices AD594x Analog Front End (AFE) controller. Its purpose is to provide a clear, structured, and condensed guide to the chip's register map and core functionalities, optimized for clarity and ease of use.

+The reference is organized by peripheral module, starting with general-purpose blocks such as I/O and timers. It then proceeds to the central AFE Controller, the watchdog and wakeup timers, and other essential hardware accelerators. The core of the document provides a detailed breakdown of the Analog Front End (AFE) block itself, covering everything from the sequencer and waveform generator to the ADC, TIA, and switch matrix. The document concludes with a practical functional example demonstrating how these registers and features are used to perform a low-frequency oscillator calibration.

+### 2.0 General Purpose I/O (AGPIO)

+The General Purpose I/O (AGPIO) module is the primary interface for configuring and controlling the AD594x's digital input/output pins. This block allows each pin to be configured for various functions, with direct control over output state, pull-up/pull-down resistors, and input path enabling. This module is crucial for tasks like triggering external events, synchronizing with other ICs, or providing simple status indicators (e.g., LEDs).

+**AGPIO_GP0CON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **GP0CON** | 0x00000000 | 0x00000000 | AGPIO GPIO Port 0 Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 14-15 | **PIN7CFG** | 0x0000C000 | P0.7 Configuration Bits |

+| 12-13 | **PIN6CFG** | 0x00003000 | P0.6 Configuration Bits |

+| 10-11 | **PIN5CFG** | 0x00000C00 | P0.5 Configuration Bits |

+| 8-9 | **PIN4CFG** | 0x00000300 | P0.4 Configuration Bits |

+| 6-7 | **PIN3CFG** | 0x000000C0 | P0.3 Configuration Bits |

+| 4-5 | **PIN2CFG** | 0x00000030 | P0.2 Configuration Bits |

+| 2-3 | **PIN1CFG** | 0x0000000C | P0.1 Configuration Bits |

+| 0-1 | **PIN0CFG** | 0x00000003 | P0.0 Configuration Bits |

+**AGPIO_GP0OEN**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **GP0OEN** | 0x00000004 | 0x00000000 | AGPIO GPIO Port 0 Output Enable |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **OEN** | 0x000000FF | Pin Output Drive Enable |

+**AGPIO_GP0PE**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **GP0PE** | 0x00000008 | 0x00000000 | AGPIO GPIO Port 0 Pull-up/Pull-down Enable |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **PE** | 0x000000FF | Pin Pull Enable |

+**AGPIO_GP0IEN**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **GP0IEN** | 0x0000000C | 0x00000000 | AGPIO GPIO Port 0 Input Path Enable |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **IEN** | 0x000000FF | Input Path Enable |

+**AGPIO_GP0IN**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **GP0IN** | 0x00000010 | 0x00000000 | AGPIO GPIO Port 0 Registered Data Input |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **IN** | 0x000000FF | Registered Data Input |

+**AGPIO_GP0OUT**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **GP0OUT** | 0x00000014 | 0x00000000 | AGPIO GPIO Port 0 Data Output |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **OUT** | 0x000000FF | Data Out |

+**AGPIO_GP0SET**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **GP0SET** | 0x00000018 | 0x00000000 | AGPIO GPIO Port 0 Data Out Set |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **SET** | 0x000000FF | Set the Output HIGH |

+**AGPIO_GP0CLR**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **GP0CLR** | 0x0000001C | 0x00000000 | AGPIO GPIO Port 0 Data Out Clear |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **CLR** | 0x000000FF | Set the Output LOW |

+**AGPIO_GP0TGL**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **GP0TGL** | 0x00000020 | 0x00000000 | AGPIO GPIO Port 0 Pin Toggle |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **TGL** | 0x000000FF | Toggle the Output |

+These registers provide a comprehensive interface for managing the digital I/O pins, transitioning next to the core AFE controller block.

+### 3.0 AFE Controller (AFECON)

+The AFE Controller (AFECON) module is the central control block for the entire AFE. It is responsible for fundamental operations such as chip identification, system and Analog-to-Digital Converter (ADC) clock configuration, software resets, and triggering measurement sequences.

+**AFECON_ADIID**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **ADIID** | 0x00000400 | 0x00000000 | ADI Identification |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **ADIID** | 0x0000FFFF | ADI Identifier. |

+**AFECON_CHIPID**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CHIPID** | 0x00000404 | 0x00000000 | Chip Identification |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 4-15 | **PARTID** | 0x0000FFF0 | Part Identifier |

+| 0-3 | **REVISION** | 0x0000000F | Silicon Revision Number |

+**AFECON_CLKCON0**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CLKCON0** | 0x00000408 | 0x00000441 | Clock Divider Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 10-15 | **SFFTCLKDIVCNT** | 0x0000FC00 | SFFT Clock Divider Configuration |

+| 6-9 | **ADCCLKDIV** | 0x000003C0 | ADC Clock Divider Configuration |

+| 0-5 | **SYSCLKDIV** | 0x0000003F | System Clock Divider Configuration |

+**AFECON_CLKEN1**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CLKEN1** | 0x00000410 | 0x000002C0 | Clock Gate Enable |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 7 | **GPT1DIS** | 0x00000080 | GPT1 Clock Enable |

+| 6 | **GPT0DIS** | 0x00000040 | GPT0 Clock Enable |

+| 5 | **ACLKDIS** | 0x00000020 | ACLK Clock Enable |

+**AFECON_CLKSEL**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CLKSEL** | 0x00000414 | 0x00000000 | Clock Select |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 2-3 | **ADCCLKSEL** | 0x0000000C | Select ADC Clock Source |

+| 0-1 | **SYSCLKSEL** | 0x00000003 | Select System Clock Source |

+**AFECON_CLKCON0KEY**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CLKCON0KEY** | 0x00000420 | 0x00000000 | Enable Clock Division to 8Mhz, 4Mhz and 2Mhz |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **DIVSYSCLK_ULP_EN** | 0x0000FFFF | Enable Clock Division to 8Mhz, 4Mhz and 2Mhz |

+**AFECON_SWRSTCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **SWRSTCON** | 0x00000424 | 0x00000001 | Software Reset |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **SWRSTL** | 0x0000FFFF | Software Reset |

+**AFECON_TRIGSEQ**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **TRIGSEQ** | 0x00000430 | 0x00000000 | Trigger Sequence |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 3 | **TRIG3** | 0x00000008 | Trigger Sequence 3 |

+| 2 | **TRIG2** | 0x00000004 | Trigger Sequence 2 |

+| 1 | **TRIG1** | 0x00000002 | Trigger Sequence 1 |

+| 0 | **TRIG0** | 0x00000001 | Trigger Sequence 0 |

+With the central controller defined, the next section covers the system's safety watchdog timer.

+### 4.0 AFE Watchdog Timer (AFEWDT)

+The AFE Watchdog Timer (AFEWDT) is a critical safety feature designed to monitor system operation. It can be configured to trigger a system reset or generate an interrupt if the application software fails to refresh it within a specified time period, preventing the system from becoming unresponsive.

+**AFEWDT_WDTLD**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WDTLD** | 0x00000900 | Undefined | Watchdog Timer Load Value |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **LOAD** | 0x0000FFFF | WDT Load Value |

+**AFEWDT_WDTVALS**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WDTVALS** | 0x00000904 | Undefined | Current Count Value |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **CCOUNT** | 0x0000FFFF | Current WDT Count Value. |

+**AFEWDT_WDTCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WDTCON** | 0x00000908 | Undefined | Watchdog Timer Control Register |

+| Bit Position(s) | Bitfield Name | Bitmask | Description | Settings/Enumerations |

+|---|---|---|---|---|

+| 10 | **WDTIRQEN** | 0x00000400 | WDT Interrupt Enable | |

+| 9 | **MINLOAD_EN** | 0x00000200 | Timer Window Control | |

+| 8 | **CLKDIV2** | 0x00000100 | Clock Source | |

+| 6 | **MDE** | 0x00000040 | Timer Mode Select | |

+| 5 | **EN** | 0x00000020 | Timer Enable | |

+| 2-3 | **PRE** | 0x0000000C | Prescaler. | |

+| 1 | **IRQ** | 0x00000002 | WDT Interrupt Enable | 0 **(RESET):** Watchdog timer timeout creates a reset.

1 **(INTERRUPT):** Watchdog timer timeout creates an interrupt. |

+| 0 | **PDSTOP** | 0x00000001 | Power Down Stop Enable | 0 **(CONTINUE):** Continue counting in Hibernate mode.

1 **(STOP):** Stop counter in Hibernate mode. |

+**AFEWDT_WDTCLRI**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WDTCLRI** | 0x0000090C | Undefined | Refresh Watchdog Register |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **CLRWDG** | 0x0000FFFF | Refresh Register |

+**AFEWDT_WDTSTA**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WDTSTA** | 0x00000918 | Undefined | Timer Status |

+| Bit Position(s) | Bitfield Name | Bitmask | Description | Settings/Enumerations |

+|---|---|---|---|---|

+| 6 | **TMINLD** | 0x00000040 | WDTMINLD Write Status | |

+| 5 | **OTPWRDONE** | 0x00000020 | Reset Type Status | |

+| 4 | **LOCK** | 0x00000010 | Lock Status | 0 **(OPEN):** Timer operation is not locked.

1 **(LOCKED):** Timer is enabled and locked. |

+| 3 | **CON** | 0x00000008 | WDTCON Write Status | |

+| 2 | **TLD** | 0x00000004 | WDTVAL Write Status | 0 **(SYNC_COMPLETE):** WDTLD values match across clock domains.

1 **(SYNC_IN_PROGRESS):** Synchronize in progress. |

+| 1 | **CLRI** | 0x00000002 | WDTCLRI Write Status | |

+| 0 | **IRQ** | 0x00000001 | WDT Interrupt | 0 **(CLEARED):** Watchdog timer interrupt is not pending.

1 **(PENDING):** Watchdog timer interrupt is pending. |

+**AFEWDT_WDTMINLD**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WDTMINLD** | 0x0000091C | Undefined | Minimum Load Value |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **MIN_LOAD** | 0x0000FFFF | WDT Min Load Value |

+Complementing the watchdog is the low-power wakeup timer, which enables periodic operation.

+### 5.0 Wakeup Timer (WUPTMR)

+The Wakeup Timer (WUPTMR) is a strategic peripheral for managing low-power sleep and wake cycles. It enables the AD594x to enter a low-power hibernate state and wake up at precise, user-defined intervals to execute measurement sequences. This functionality is crucial for applications requiring periodic measurements with high precision while minimizing power consumption.

+**WUPTMR_CON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CON** | 0x00000800 | 0x00000000 | Timer Control |

+| Bit Position(s) | Bitfield Name | Bitmask | Description | Settings/Enumerations |

+|---|---|---|---|---|

+| 6 | **MSKTRG** | 0x00000040 | Mark Sequence Trigger from Sleep Wakeup Timer | |

+| 4-5 | **CLKSEL** | 0x00000030 | Clock Selection | 0x0 **(SWT32K0):** Internal 32kHz OSC

0x1 **(SWTEXT0):** External Clock

0x2 **(SWT32K):** Internal 32kHz OSC

0x3 **(SWTEXT):** External Clock |

+| 1-3 | **ENDSEQ** | 0x0000000E | End Sequence | 0x0 **(ENDSEQA):** Stop at SeqA, loop to SeqA

0x1 **(ENDSEQB):** Stop at SeqB, loop to SeqA

0x2 **(ENDSEQC):** Stop at SeqC, loop to SeqA

0x3 **(ENDSEQD):** Stop at SeqD, loop to SeqA

0x4 **(ENDSEQE):** Stop at SeqE, loop to SeqA

0x5 **(ENDSEQF):** Stop at SeqF, loop to SeqA

0x6 **(ENDSEQG):** Stop at SeqG, loop to SeqA

0x7 **(ENDSEQH):** Stop at SeqH, loop to SeqA |

+| 0 | **EN** | 0x00000001 | Sleep Wake Timer Enable Bit | 0 **(SWTEN):** Enable Sleep Wakeup Timer

1 **(SWTDIS):** Disable Sleep Wakeup Timer |

+**WUPTMR_SEQORDER**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **SEQORDER** | 0x00000804 | 0x00000000 | Order Control |

+| Bit Position(s) | Bitfield Name | Bitmask | Description | Settings/Enumerations |

+|---|---|---|---|---|

+| 14-15 | **SEQH** | 0x0000C000 | SEQH Config | 0x0 **(SEQH0):** Fill SEQ0 In

0x1 **(SEQH1):** Fill SEQ1 In

0x2 **(SEQH2):** Fill SEQ2 In

0x3 **(SEQH3):** Fill SEQ3 In |

+| 12-13 | **SEQG** | 0x00003000 | SEQG Config | 0x0 **(SEQG0):** Fill SEQ0 In

0x1 **(SEQG1):** Fill SEQ1 In

0x2 **(SEQG2):** Fill SEQ2 In

0x3 **(SEQG3):** Fill SEQ3 In |

+| 10-11 | **SEQF** | 0x00000C00 | SEQF Config | 0x0 **(SEQF0):** Fill SEQ0 In

0x1 **(SEQF1):** Fill SEQ1 In

0x2 **(SEQF2):** Fill SEQ2 In

0x3 **(SEQF3):** Fill SEQ3 In |

+| 8-9 | **SEQE** | 0x00000300 | SEQE Config | 0x0 **(SEQE0):** Fill SEQ0 In

0x1 **(SEQE1):** Fill SEQ1 In

0x2 **(SEQE2):** Fill SEQ2 In

0x3 **(SEQE3):** Fill SEQ3 In |

+| 6-7 | **SEQD** | 0x000000C0 | SEQD Config | 0x0 **(SEQD0):** Fill SEQ0 In

0x1 **(SEQD1):** Fill SEQ1 In

0x2 **(SEQD2):** Fill SEQ2 In

0x3 **(SEQD3):** Fill SEQ3 In |

+| 4-5 | **SEQC** | 0x00000030 | SEQC Config | 0x0 **(SEQC0):** Fill SEQ0 In

0x1 **(SEQC1):** Fill SEQ1 In

0x2 **(SEQC2):** Fill SEQ2 In

0x3 **(SEQC3):** Fill SEQ3 In |

+| 2-3 | **SEQB** | 0x0000000C | SEQB Config | 0x0 **(SEQB0):** Fill SEQ0 In

0x1 **(SEQB1):** Fill SEQ1 In

0x2 **(SEQB2):** Fill SEQ2 In

0x3 **(SEQB3):** Fill SEQ3 In |

+| 0-1 | **SEQA** | 0x00000003 | SEQA Config | 0x0 **(SEQA0):** Fill SEQ0 In

0x1 **(SEQA1):** Fill SEQ1 In

0x2 **(SEQA2):** Fill SEQ2 In

0x3 **(SEQA3):** Fill SEQ3 In |

+**WUPTMR_SEQxWUP / SEQxSLEEP Registers**

+The timer provides four sets of registers for defining sleep and active periods for different sequences. These register pairs define the 20-bit sleep and active (wakeup) periods for each of the four sequences (0-3).

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **SEQ0WUPL** | 0x00000808 | 0x0000FFFF | SEQ0 Wakeup Time (LSB) |

+| **SEQ0WUPH** | 0x0000080C | 0x0000000F | SEQ0 Wakeup Time (MSB) |

+| **SEQ0SLEEPL** | 0x00000810 | 0x0000FFFF | SEQ0 Sleep Time (LSB) |

+| **SEQ0SLEEPH** | 0x00000814 | 0x0000000F | SEQ0 Sleep Time (MSB) |

+| **SEQ1WUPL** | 0x00000818 | 0x0000FFFF | SEQ1 Wakeup Time (LSB) |

+| **SEQ1WUPH** | 0x0000081C | 0x0000000F | SEQ1 Wakeup Time (MSB) |

+| **SEQ1SLEEPL** | 0x00000820 | 0x0000FFFF | SEQ1 Sleep Time (LSB) |

+| **SEQ1SLEEPH** | 0x00000824 | 0x0000000F | SEQ1 Sleep Time (MSB) |

+| **SEQ2WUPL** | 0x00000828 | 0x0000FFFF | SEQ2 Wakeup Time (LSB) |

+| **SEQ2WUPH** | 0x0000082C | 0x0000000F | SEQ2 Wakeup Time (MSB) |

+| **SEQ2SLEEPL** | 0x00000830 | 0x0000FFFF | SEQ2 Sleep Time (LSB) |

+| **SEQ2SLEEPH** | 0x00000834 | 0x0000000F | SEQ2 Sleep Time (MSB) |

+| **SEQ3WUPL** | 0x00000838 | 0x0000FFFF | SEQ3 Wakeup Time (LSB) |

+| **SEQ3WUPH** | 0x0000083C | 0x0000000F | SEQ3 Wakeup Time (MSB) |

+| **SEQ3SLEEPL** | 0x00000840 | 0x0000FFFF | SEQ3 Sleep Time (LSB) |

+| **SEQ3SLEEPH** | 0x00000844 | 0x0000000F | SEQ3 Sleep Time (MSB) |

+The wakeup timer relies on the fundamental clock sources and power modes managed by the Always-On register block.

+### 6.0 Always-On Registers (ALLON)

+The Always-On (ALLON) register block controls the most fundamental aspects of the chip's operation. These registers manage power modes, core oscillators, and reset status, and their settings persist even when the chip is in its lowest power states.

+**ALLON_PWRMOD**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **PWRMOD** | 0x00000A00 | 0x00000001 | Power Modes |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 15 | **RAMRETEN** | 0x00008000 | Retention for RAM |

+| 14 | **ADCRETEN** | 0x00004000 | Keep ADC Power Switch on in Hibernate |

+| 3 | **SEQSLPEN** | 0x00000008 | Auto Sleep by Sequencer Command |

+| 2 | **TMRSLPEN** | 0x00000004 | Auto Sleep by Sleep Wakeup Timer |

+| 0-1 | **PWRMOD** | 0x00000003 | Power Mode Control Bits |

+**ALLON_OSCCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **OSCCON** | 0x00000A10 | 0x00000003 | Oscillator Control |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 10 | **HFXTALOK** | 0x00000400 | Status of HFXTAL Oscillator |

+| 9 | **HFOSCOK** | 0x00000200 | Status of HFOSC Oscillator |

+| 8 | **LFOSCOK** | 0x00000100 | Status of LFOSC Oscillator |

+| 2 | **HFXTALEN** | 0x00000004 | High Frequency Crystal Oscillator Enable |

+| 1 | **HFOSCEN** | 0x00000002 | High Frequency Internal Oscillator Enable |

+| 0 | **LFOSCEN** | 0x00000001 | Low Frequency Internal Oscillator Enable |

+**ALLON_RSTSTA**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **RSTSTA** | 0x00000A40 | 0x00000000 | Reset Status |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 4 | **PINSWRST** | 0x00000010 | Software Reset Pin |

+| 3 | **MMRSWRST** | 0x00000008 | MMR Software Reset |

+| 2 | **WDRST** | 0x00000004 | Watchdog Timeout |

+| 1 | **EXTRST** | 0x00000002 | External Reset |

+| 0 | **POR** | 0x00000001 | Power-on Reset |

+**ALLON_CLKEN0**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CLKEN0** | 0x00000A70 | 0x00000004 | 32KHz Peripheral Clock Enable |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 2 | **TIACHPDIS** | 0x00000004 | TIA Chop Clock Disable |

+| 1 | **SLPWUTDIS** | 0x00000002 | Sleep/Wakeup Timer Clock Disable |

+| 0 | **WDTDIS** | 0x00000001 | Watch Dog Timer Clock Disable |

+These core settings provide the foundation for higher-level peripherals, such as the general-purpose timers.

+### 7.0 General Purpose Timers (AGPT0 & AGPT1)

+The AD594x includes two 16-bit general-purpose timers, AGPT0 and AGPT1. These timers are highly configurable and can be used for a variety of tasks, including event timing, generating interrupts, signal capture, and Pulse Width Modulation (PWM) generation.

+**7.1 Timer 0 (AGPT0)**

+**AGPT0_LD0**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **LD0** | 0x00000D00 | Undefined | 16-bit Load Value Register. |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **LOAD** | 0x0000FFFF | Load Value |

+**AGPT0_VAL0**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **VAL0** | 0x00000D04 | Undefined | 16-Bit Timer Value Register. |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **VAL** | 0x0000FFFF | Current Count |

+**AGPT0_CON0**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CON0** | 0x00000D08 | Undefined | Control Register. |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 15 | **SYNCBYP** | 0x00008000 | Synchronization Bypass |

+| 14 | **RSTEN** | 0x00004000 | Counter and Prescale Reset Enable |

+| 13 | **EVTEN** | 0x00002000 | Event Select |

+| 8-12 | **EVENT** | 0x00001F00 | Event Select Range |

+| 7 | **RLD** | 0x00000080 | Reload Control |

+| 5-6 | **CLK** | 0x00000060 | Clock Select |

+| 4 | **ENABLE** | 0x00000010 | Timer Enable |

+| 3 | **MOD** | 0x00000008 | Timer Mode |

+| 2 | **UP** | 0x00000004 | Count up |

+| 0-1 | **PRE** | 0x00000003 | Prescaler |

+**AGPT0_PWMCON0**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **PWMCON0** | 0x00000D20 | Undefined | PWM Control Register. |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 1 | **IDLE** | 0x00000002 | PWM Idle State |

+| 0 | **MATCHEN** | 0x00000001 | PWM Match Enabled |

+**AGPT0_PWMMAT0**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **PWMMAT0** | 0x00000D24 | Undefined | PWM Match Value Register. |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **MATCHVAL** | 0x0000FFFF | PWM Match Value |

+**7.2 Timer 1 (AGPT1)**

+**AGPT1_LD1**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **LD1** | 0x00000E00 | Undefined | 16-bit Load Value Register |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **LOAD** | 0x0000FFFF | Load Value |

+**AGPT1_VAL1**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **VAL1** | 0x00000E04 | Undefined | 16-bit Timer Value Register |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **VAL** | 0x0000FFFF | Current Count |

+**AGPT1_CON1**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CON1** | 0x00000E08 | Undefined | Control Register |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 15 | **SYNCBYP** | 0x00008000 | Synchronization Bypass |

+| 14 | **RSTEN** | 0x00004000 | Counter and Prescale Reset Enable |

+| 13 | **EVENTEN** | 0x00002000 | Event Select |

+| 8-12 | **EVENT** | 0x00001F00 | Event Select Range |

+| 7 | **RLD** | 0x00000080 | Reload Control |

+| 5-6 | **CLK** | 0x00000060 | Clock Select |

+| 4 | **ENABLE** | 0x00000010 | Timer Enable |

+| 3 | **MOD** | 0x00000008 | Timer Mode |

+| 2 | **UP** | 0x00000004 | Count up |

+| 0-1 | **PRE** | 0x00000003 | Prescaler |

+**AGPT1_PWMCON1**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **PWMCON1** | 0x00000E20 | Undefined | PWM Control Register |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 1 | **IDLE** | 0x00000002 | PWM Idle State. |

+| 0 | **MATCHEN** | 0x00000001 | PWM Match Enabled. |

+**AGPT1_PWMMAT1**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **PWMMAT1** | 0x00000E24 | Undefined | PWM Match Value Register |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **MATCHVAL** | 0x0000FFFF | PWM Match Value |

+For data integrity tasks, the device includes a dedicated hardware accelerator.

+

+## 8.0 Switch Matrix & Electrode Connections (SWMAT)

+The AD5940 features a highly flexible switch matrix that routes external electrode signals (SE0, RE0, CE0, AINx) to internal blocks like the High-Speed DAC (Excitation), the ADC, and the TIA. The matrix is divided into four main blocks: **D** (DAC/Excitation), **P** (Positive Input), **N** (Negative Input), and **T** (TIA/Transimpedance).

+**8.1 Core Switch Registers**

+These registers provide direct control over every switch in the matrix.

+**AFE_SWCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **SWCON** | 0x0000200C | 0x0000FFFF | Master Switch Matrix Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 12-15 | **TMUXCON** | 0x0000F000 | Control of T Switch MUX |

+| 8-11 | **NMUXCON** | 0x00000F00 | Control of N Switch MUX |

+| 4-7 | **PMUXCON** | 0x000000F0 | Control of P Switch MUX |

+| 0-3 | **DMUXCON** | 0x0000000F | Control of D Switch MUX |

+**AFE_DSWFULLCON (Excitation/DAC Path)**

+Controls switches connecting pins to the Excitation Loop (High-Speed DAC output).

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **DSWFULLCON** | 0x00002150 | 0x00000000 | D-Block Switch Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Connection/Description |

+|---|---|---|---|

+| 7 | **D8** | 0x00000080 | Connects **SE0** to D-Node |

+| 6 | **D7** | 0x00000040 | Connects **CE0** to D-Node |

+| 5 | **D6** | 0x00000020 | Connects **RE0** to D-Node |

+| 4 | **D5** | 0x00000010 | Connects **AIN3** to D-Node |

+| 3 | **D4** | 0x00000008 | Connects **AIN2** to D-Node |

+| 2 | **D3** | 0x00000004 | Connects **AIN1** to D-Node |

+| 1 | **D2** | 0x00000002 | Connects **AIN0** to D-Node |

+| 0 | **DR0** | 0x00000001 | Connects **RCAL0** to D-Node |

+**AFE_PSWFULLCON (Positive Input Path)**

+Controls switches connecting pins to the Positive Input bus (ADC P-Input, etc.).

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **PSWFULLCON** | 0x00002154 | 0x00000000 | P-Block Switch Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Connection/Description |

+|---|---|---|---|

+| 14 | **PL2** | 0x00004000 | Connects **CE0** to P-Node |

+| 13 | **PL** | 0x00002000 | Connects **SE0** to P-Node |

+| 11 | **P12** | 0x00000800 | Connects **DE0** to P-Node |

+| 10 | **P11** | 0x00000400 | Connects **RE0** to P-Node |

+| 4 | **P5** | 0x00000010 | Connects **AIN3** to P-Node |

+| 3 | **P4** | 0x00000008 | Connects **AIN2** to P-Node |

+| 2 | **P3** | 0x00000004 | Connects **AIN1** to P-Node |

+| 1 | **P2** | 0x00000002 | Connects **AIN0** to P-Node |

+| 0 | **PR0** | 0x00000001 | Connects **RCAL0** to P-Node |

+**AFE_NSWFULLCON (Negative Input Path)**

+Controls switches connecting pins to the Negative Input bus (ADC N-Input, TIA Input).

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **NSWFULLCON** | 0x00002158 | 0x00000000 | N-Block Switch Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Connection/Description |

+|---|---|---|---|

+| 11 | **NL2** | 0x00000800 | Connects **CE0** to N-Node |

+| 10 | **NL** | 0x00000400 | Connects **SE0** to N-Node |

+| 8 | **N9** | 0x00000100 | Connects **DE0** to N-Node |

+| 7 | **N8** | 0x00000080 | Connects **RE0** to N-Node |

+| 4 | **N5** | 0x00000010 | Connects **AIN3** to N-Node |

+| 3 | **N4** | 0x00000008 | Connects **AIN2** to N-Node |

+| 2 | **N3** | 0x00000004 | Connects **AIN1** to N-Node |

+| 1 | **N2** | 0x00000002 | Connects **AIN0** to N-Node |

+| 0 | **NR1** | 0x00000200 | Connects **RCAL0** to N-Node |

+**AFE_TSWFULLCON (TIA Feedback Path)**

+Controls switches connecting pins primarily for TIA feedback loops.

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **TSWFULLCON** | 0x0000215C | 0x00000000 | T-Block Switch Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Connection/Description |

+|---|---|---|---|

+| 10 | **T11** | 0x00000400 | **SE0** T-Switch (Often used for SE0-RE0 Short) |

+| 9 | **T10** | 0x00000200 | **DE0** T-Switch |

+| 8 | **T9** | 0x00000100 | **RE0** T-Switch |

+| 6 | **T7** | 0x00000040 | **AIN3** T-Switch |

+| 4 | **T5** | 0x00000010 | **AIN2** T-Switch |

+| 3 | **T4** | 0x00000008 | **AIN1** T-Switch |

+| 2 | **T3** | 0x00000004 | **AIN0** T-Switch |

+| 1 | **T2** | 0x00000002 | **RCAL0** T-Switch |

+**8.2 Shorting SE0 to RE0 (LPTIA Switch)**

+While the TSWFULLCON register contains bit **T11** (associated with SE0), the specific functionality to short **SE0** to **RE0** is explicitly defined as a macro configuration in the Low Power TIA Switch register. This closes internal switch **SW11**.

+**AFE_LPTIASW0**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **LPTIASW0** | 0x000020E4 | 0x00000000 | LPTIA Channel 0 Switch Config |

+**Key Configuration for SE0-RE0 Short:**

+* **Bitmask**: 0x00000800

+* **Enum Name**: ENUM_AFE_LPTIASWO_SESHORTRE

+* **Description**: Closes **SW11**. This physically shorts the Sense Electrode 0 (SE0) to the Reference Electrode 0 (RE0). This is commonly used in 2-wire measurement modes or specific sensor biasing configurations.

+

+⠀**8.3 Electrode Pin Capability Summary**

+| **Pin Name** | **Can Source (DAC)?** | **Can Sink (TIA)?** | **Can Sense (ADC P/N)?** | **Relevant Switches** |

+|---|---|---|---|---|

+| **CE0** | Yes (via D7) | Yes (via NL2) | Yes (via PL2/NL2) | D7, PL2, NL2 |

+| **RE0** | Yes (via D6) | Yes (via N8) | Yes (via P11/N8) | D6, P11, N8, T9 |

+| **SE0** | Yes (via D8) | Yes (via NL) | Yes (via PL/NL) | D8, PL, NL, T11 |

+| **AIN0-3** | Yes (via D2-D5) | Yes (via N2-N5) | Yes (via P2-P5) | D2-D5, P2-P5, N2-N5 |

+| **RCAL0** | Yes (via DR0) | Yes (via NR1) | Yes (via PR0) | DR0, PR0, NR1 |

+

+

+### 9.0 CRC Accelerator (AFECRC)

+The AFECRC module is a dedicated hardware accelerator for calculating Cyclic Redundancy Checks (CRC). This feature is essential for ensuring data integrity, allowing for fast and efficient error-checking of memory contents (like the sequencer command SRAM) or communication data without burdening the host processor.

+**AFECRC_CTL**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CTL** | 0x00001000 | Undefined | CRC Control Register |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 4 | **W16SWP** | 0x00000010 | Word16 Swap Enabled. |

+| 3 | **BYTMIRR** | 0x00000008 | Byte Mirroring. |

+| 2 | **BITMIRR** | 0x00000004 | Bit Mirroring. |

+| 1 | **LSBFIRST** | 0x00000002 | LSB First Calculation Order |

+| 0 | **EN** | 0x00000001 | CRC Peripheral Enable |

+**AFECRC_IPDATA**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **IPDATA** | 0x00001004 | Undefined | Data Input. |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-31 | **VALUE** | 0xFFFFFFFF | Data Input. |

+**AFECRC_RESULT**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **RESULT** | 0x00001008 | Undefined | CRC Residue |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-31 | **VALUE** | 0xFFFFFFFF | CRC Residue |

+**AFECRC_POLY**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **POLY** | 0x0000100C | Undefined | CRC Reduction Polynomial |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-31 | **VALUE** | 0xFFFFFFFF | CRC Reduction Polynomial |

+**AFECRC_IPBITS**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **IPBITS** | 0x00001010 | Undefined | Input Data Bits |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **DATA_BITS** | 0x000000FF | Input Data Bits. |

+**AFECRC_IPBYTE**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **IPBYTE** | 0x00001014 | Undefined | Input Data Byte |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **DATA_BYTE** | 0x000000FF | Input Data Byte. |

+**AFECRC_CRC_SIG_COMP**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CRC_SIG_COMP** | 0x00001020 | Undefined | CRC Signature Compare Data Input |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-31 | **CRC_SIG** | 0xFFFFFFFF | CRC Signature Compare Data Input. |

+**AFECRC_CRCINTEN**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **CRCINTEN** | 0x00001024 | Undefined | CRC Error Interrupt Enable |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0 | **CRC_ERR_EN** | 0x00000001 | CRC Error Interrupt Enable Bit |

+**AFECRC_INTSTA**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **INTSTA** | 0x00001028 | Undefined | CRC Error Interrupt Status |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0 | **CRC_ERR_ST** | 0x00000001 | CRC Error Interrupt Status Bit |

+The next section details the main Analog Front End, which integrates all measurement capabilities.

+### 10.0 Analog Front End Core (AFE)

+The AFE block is the heart of the AD594x, integrating all the high-performance analog and digital components required for advanced electrochemical and bioimpedance measurements. This comprehensive module contains the high-speed and low-power Digital-to-Analog Converters (DACs) and Transimpedance Amplifiers (TIAs), the ADC and its associated digital filters, the powerful command sequencer with its data and command FIFOs, and the flexible switch matrix that routes signals between the analog blocks and external pins.

+**10.1 Core and Sequencer Configuration**

+**AFE_AFECON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **AFECON** | 0x00002000 | 0x00080000 | AFE Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 21 | **DACBUFEN** | 0x00200000 | Enable DC DAC Buffer |

+| 20 | **DACREFEN** | 0x00100000 | High Speed DAC Reference Enable |

+| 19 | **ALDOILIMITEN** | 0x00080000 | Analog LDO Current Limiting Enable |

+| 16 | **SINC2EN** | 0x00010000 | ADC Output 50/60Hz Filter Enable |

+| 15 | **DFTEN** | 0x00008000 | DFT Hardware Accelerator Enable |

+| 14 | **WAVEGENEN** | 0x00004000 | Waveform Generator Enable |

+| 13 | **TEMPCONVEN** | 0x00002000 | ADC Temp Sensor Convert Enable |

+| 12 | **TEMPSENSEN** | 0x00001000 | ADC Temperature Sensor Channel Enable |

+| 11 | **TIAEN** | 0x00000800 | High Power TIA Enable |

+| 10 | **INAMPEN** | 0x00000400 | Enable Excitation Amplifier |

+| 9 | **EXBUFEN** | 0x00000200 | Enable Excitation Buffer |

+| 8 | **ADCCONVEN** | 0x00000100 | ADC Conversion Start Enable |

+| 7 | **ADCEN** | 0x00000080 | ADC Power Enable |

+| 6 | **DACEN** | 0x00000040 | High Power DAC Enable |

+| 5 | **HPREFDIS** | 0x00000020 | Disable High Power Reference |

+**AFE_SEQCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **SEQCON** | 0x00002004 | 0x00000002 | Sequencer Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 8-15 | **SEQWRTMR** | 0x0000FF00 | Timer for Sequencer Write Commands |

+| 4 | **SEQHALT** | 0x00000010 | Halt Seq |

+| 1 | **SEQHALTFIFOEMPTY** | 0x00000002 | Halt Sequencer If Empty |

+| 0 | **SEQEN** | 0x00000001 | Enable Sequencer |

+**AFE_FIFOCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **FIFOCON** | 0x00002008 | 0x00001010 | FIFOs Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 13-15 | **DATAFIFOSRCSEL** | 0x0000E000 | Selects the Source for the Data FIFO. |

+| 11 | **DATAFIFOEN** | 0x00000800 | Data FIFO Enable. |

+**AFE_SEQCRC**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **SEQCRC** | 0x00002060 | 0x00000001 | Sequencer CRC Value |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-7 | **CRC** | 0x000000FF | Sequencer Command CRC Value. |

+**AFE_SEQCNT**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **SEQCNT** | 0x00002064 | 0x00000000 | Sequencer Command Count |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-15 | **COUNT** | 0x0000FFFF | Sequencer Command Count |

+**AFE_SEQTIMEOUT**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **SEQTIMEOUT** | 0x00002068 | 0x00000000 | Sequencer Timeout Counter |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-29 | **TIMEOUT** | 0x3FFFFFFF | Current Value of the Sequencer Timeout Counter. |

+**10.2 Waveform Generator**

+**AFE_WGCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WGCON** | 0x00002014 | 0x00000030 | Waveform Generator Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 5 | **DACGAINCAL** | 0x00000020 | Bypass DAC Gain |

+| 4 | **DACOFFSETCAL** | 0x00000010 | Bypass DAC Offset |

+| 1-2 | **TYPESEL** | 0x00000006 | Selects the Type of Waveform |

+| 0 | **TRAPRSTEN** | 0x00000001 | Resets the Trapezoid Waveform Generator |

+**AFE_WGFCW**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WGFCW** | 0x00002030 | 0x00000000 | Waveform Generator - Sinusoid Frequency Control Word |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-23 | **SINEFCW** | 0x00FFFFFF | Sinusoid Generator Frequency Control Word |

+**AFE_WGPHASE**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WGPHASE** | 0x00002034 | 0x00000000 | Waveform Generator - Sinusoid Phase Offset |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-19 | **SINEOFFSET** | 0x000FFFFF | Sinusoid Phase Offset |

+**AFE_WGOFFSET**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WGOFFSET** | 0x00002038 | 0x00000000 | Waveform Generator - Sinusoid Offset |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-11 | **SINEOFFSET** | 0x00000FFF | Sinusoid Offset |

+**AFE_WGAMPLITUDE**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WGAMPLITUDE** | 0x0000203C | 0x00000000 | Waveform Generator - Sinusoid Amplitude |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 0-10 | **SINEAMPLITUDE** | 0x000007FF | Sinusoid Amplitude |

+**Trapezoid Waveform Registers**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **WGDCLEVEL1** | 0x00002018 | 0x00000000 | Waveform Generator - Trapezoid DC Level 1 |

+| **WGDCLEVEL2** | 0x0000201C | 0x00000000 | Waveform Generator - Trapezoid DC Level 2 |

+| **WGDELAY1** | 0x00002020 | 0x00000000 | Waveform Generator - Trapezoid Delay 1 Time |

+| **WGSLOPE1** | 0x00002024 | 0x00000000 | Waveform Generator - Trapezoid Slope 1 Time |

+| **WGDELAY2** | 0x00002028 | 0x00000000 | Waveform Generator - Trapezoid Delay 2 Time |

+| **WGSLOPE2** | 0x0000202C | 0x00000000 | Waveform Generator - Trapezoid Slope 2 Time |

+**10.3 ADC, Filters, and Data Path**

+**AFE_ADCFILTERCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **ADCFILTERCON** | 0x00002044 | 0x00000301 | ADC Output Filters Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 14-15 | **AVRGNUM** | 0x0000C000 | Number of Samples Averaged |

+| 12-13 | **SINC3OSR** | 0x00003000 | SINC3 OSR |

+| 8-11 | **SINC2OSR** | 0x00000F00 | SINC2 OSR |

+| 7 | **AVRGEN** | 0x00000080 | Average Function Enable |

+| 6 | **SINC3BYP** | 0x00000040 | SINC3 Filter Bypass |

+| 0 | **ADCCLK** | 0x00000001 | ADC Data Rate |

+**AFE_ADCCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **ADCCON** | 0x000021A8 | 0x00000000 | ADC Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 16-18 | **GNPGA** | 0x00070000 | PGA Gain Setup |

+| 15 | **GNOFSELPGA** | 0x00008000 | Internal Offset/Gain Cancellation |

+| 8-12 | **MUXSELN** | 0x00001F00 | Select Negative Input |

+| 0-5 | **MUXSELP** | 0x0000003F | Select Positive Input |

+**AFE_DFTCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **DFTCON** | 0x000020D0 | 0x00000090 | AFE DSP Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 20-21 | **DFTINSEL** | 0x00300000 | DFT Input Select |

+| 4-7 | **DFTNUM** | 0x000000F0 | ADC Samples Used |

+| 0 | **HANNINGEN** | 0x00000001 | Hanning Window Enable |

+**Data and FIFO Registers**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **ADCDAT** | 0x00002074 | 0x00000000 | ADC Raw Result |

+| **DFTREAL** | 0x00002078 | 0x00000000 | DFT Result, Real Part |

+| **DFTIMAG** | 0x0000207C | 0x00000000 | DFT Result, Imaginary Part |

+| **SINC2DAT** | 0x00002080 | 0x00000000 | Supply Rejection Filter Result |

+| **TEMPSENSDAT** | 0x00002084 | 0x00000000 | Temperature Sensor Result |

+| **DATAFIFORD** | 0x0000206C | 0x00000000 | Data FIFO Read |

+| **CMDFIFOWRITE** | 0x00002070 | 0x00000000 | Command FIFO Write |

+**10.4 TIA and DAC Configuration**

+**High-Speed DAC and TIA**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **HSDACCON** | 0x00002010 | 0x0000001E | High Speed DAC Configuration |

+| **HSDACDAT** | 0x00002048 | 0x00000800 | HS DAC Code |

+| **HSRTIACON** | 0x000020F0 | 0x0000000F | High Power RTIA Configuration |

+| **DE0RESCON** | 0x000020F8 | 0x000000FF | DE0 HSTIA Resistors Configuration |

+| **DE1RESCON** | 0x000020F4 | Undefined | DE1 HSTIA Resistors Configuration |

+| **HSTIACON** | 0x000020FC | 0x00000000 | HSTIA Amplifier Configuration |

+**Low-Power TIA and DAC**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **LPTIACON0** | 0x000020EC | 0x00000003 | ULPTIA Control Bits Channel 0 |

+| **LPTIACON1** | 0x000020E8 | Undefined | ULPTIA Control Bits Channel 1 |

+| **LPTIASW0** | 0x000020E4 | 0x00000000 | ULPTIA Switch Configuration for Channel 0 |

+| **LPTIASW1** | 0x000020E0 | Undefined | ULPTIA Switch Configuration for Channel 1 |

+| **LPDACDAT0** | 0x00002120 | 0x00000000 | LPDAC Data-out |

+| **LPDACCON0** | 0x00002128 | 0x00000002 | LPDAC Control Bits |

+| **LPDACDAT1** | 0x0000212C | Undefined | Low Power DAC1 data register |

+| **LPDACCON1** | 0x00002134 | Undefined | ULP_DACCON1 |

+**LPTIACON0/LPTIACON1 Bitfield Breakdown**

+| Bit Position(s) | Bitfield Name | Bitmask | Description | Settings/Enumerations |

+|---|---|---|---|---|

+| 5-10 | **TIAGAIN** | 0x000003E0 | Set RTIA Gain Resistor | 0x00000000 (DISCONTIA): Disconnect

0x00000020 (TIAGAIN200): 200 Ω

0x00000040 (TIAGAIN1K): 1 kΩ

0x00000060 (TIAGAIN2K): 2 kΩ

0x00000080 (TIAGAIN3K): 3 kΩ

0x000000A0 (TIAGAIN4K): 4 kΩ

0x000000C0 (TIAGAIN6K): 6 kΩ

0x000000E0 (TIAGAIN8K): 8 kΩ

0x00000100 (TIAGAIN10K): 10 kΩ

0x00000120 (TIAGAIN12K): 12 kΩ

0x00000140 (TIAGAIN16K): 16 kΩ

0x00000160 (TIAGAIN20K): 20 kΩ

0x00000180 (TIAGAIN24K): 24 kΩ

0x000001A0 (TIAGAIN30K): 30 kΩ

0x000001C0 (TIAGAIN32K): 32 kΩ

0x000001E0 (TIAGAIN40K): 40 kΩ

0x00000200 (TIAGAIN48K): 48 kΩ

0x00000220 (TIAGAIN64K): 64 kΩ

0x00000240 (TIAGAIN85K): 85 kΩ

0x00000260 (TIAGAIN96K): 96 kΩ

0x00000280 (TIAGAIN100K): 100 kΩ

0x000002A0 (TIAGAIN120K): 120 kΩ

0x000002C0 (TIAGAIN128K): 128 kΩ

0x000002E0 (TIAGAIN160K): 160 kΩ

0x00000300 (TIAGAIN196K): 196 kΩ

0x00000320 (TIAGAIN256K): 256 kΩ

0x00000340 (TIAGAIN512K): 512 kΩ |

+| 10-12 | **TIARL** | 0x00001C00 | Set RLOAD | 0x00000000 (RL0): 0 Ω

0x00000400 (RL10): 10 Ω

0x00000800 (RL30): 30 Ω

0x00000C00 (RL50): 50 Ω

0x00001000 (RL100): 100 Ω

0x00001400 (RL1P6K): 1.6 kΩ

0x00001800 (RL3P1K): 3.1 kΩ

0x00001C00 (RL3P5K): 3.6 kΩ |

+| 13-15 | **TIARF** | 0x0000E000 | Set LPF Resistor | 0x00000000 (DISCONRF): Disconnect

0x00002000 (BYPRF): Bypass

0x00004000 (RF20K): 20 kΩ

0x00006000 (RF100K): 100 kΩ

0x00008000 (RF200K): 200 kΩ

0x0000A000 (RF400K): 400 kΩ

0x0000C000 (RF600K): 600 kΩ

0x0000E000 (RF1MOHM): 1 MΩ |

+| 1 | **PAPDEN** | 0x00000002 | PA Power Down | |

+| 0 | **TIAPDEN** | 0x00000001 | TIA Power Down | |

+**10.5 Switch Matrix**

+**AFE_SWCON**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **SWCON** | 0x0000200C | 0x0000FFFF | Switch Matrix Configuration |

+| Bit Position(s) | Bitfield Name | Bitmask | Description |

+|---|---|---|---|

+| 16 | **SWSOURCESEL** | 0x00010000 | Switch Control Select |

+| 12-15 | **TMUXCON** | 0x0000F000 | Control of T Switch MUX. |

+| 8-11 | **NMUXCON** | 0x00000F00 | Control of N Switch MUX |

+| 4-7 | **PMUXCON** | 0x000000F0 | Control of P Switch MUX |

+| 0-3 | **DMUXCON** | 0x0000000F | Control of D Switch MUX |

+**Switch Matrix Full Configuration and Status**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **DSWFULLCON** | 0x00002150 | 0x00000000 | Switch Matrix Full Configuration (D) |

+| **NSWFULLCON** | 0x00002154 | 0x00000000 | Switch Matrix Full Configuration (N) |

+| **PSWFULLCON** | 0x00002158 | 0x00000000 | Switch Matrix Full Configuration (P) |

+| **TSWFULLCON** | 0x0000215C | 0x00000000 | Switch Matrix Full Configuration (T) |

+| **DSWSTA** | 0x000021B0 | 0x00000000 | Switch Matrix Status (D) |

+| **PSWSTA** | 0x000021B4 | 0x00006000 | Switch Matrix Status (P) |

+| **NSWSTA** | 0x000021B8 | 0x00000C00 | Switch Matrix Status (N) |

+| **TSWSTA** | 0x000021BC | 0x00000000 | Switch Matrix Status (T) |

+**10.6 Power Management and Calibration**

+| Register Name | Address | Reset Value | Description |

+|---|---|---|---|

+| **PMBW** | 0x000022F0 | 0x00088800 | Power Mode Configuration |

+| **LPMODECON** | 0x00002114 | 0x00000102 | LPMODECON |

+| **LPREFBUFCON** | 0x00002050 | 0x00000000 | LPREF_BUF_CON |

+| **BUFSENCON** | 0x00002180 | 0x00000037 | HP and LP Buffer Control |

+| **ADCOFFSETHSTIA** | 0x00002234 | 0x00000000 | ADC Offset Calibration High Speed TIA Channel |

+| **ADCGNHSTIA** | 0x00002284 | 0x00004000 | ADC Gain Calibration for HS TIA Channel |

+| **DACOFFSET** | 0x00002268 | 0x00000000 | DAC Offset with Attenuator Disabled (LP Mode) |

+| **DACGAIN** | 0x00002260 | 0x00000800 | DACGAIN |

+This comprehensive set of registers enables fine-grained control over the AD594x's powerful analog capabilities. To illustrate how these are used in practice, the following section provides a functional example.

+### 11.0 Functional Example: Low Frequency Oscillator (LFOSC) Calibration

+This section provides a practical, high-level example of how the AD594x's features, particularly the sequencer and timers, are used to perform a critical task: calibrating the internal low-frequency oscillator (LFOSC).

+**11.1 Overview**

+The LFOSC is the clock source for the sleep/wakeup timer, which controls the measurement frequency of the AD5940 (i.e., how often it wakes up to run a measurement sequence). For applications that require a highly accurate and repeatable measurement sample rate, the LFOSC must be calibrated against a more precise, high-frequency clock source, such as an external 16 MHz crystal. The calibration process uses two measurement sequences to accurately measure the LFOSC period.

+**11.2 Calibration Steps**

+The calibration process involves the following sequence of operations:

+**1** **Configure Sequence A:** A sequence is created containing a single command, SEQ_TOUT(0x3fffffff), which starts the high-resolution sequencer timeout counter. This sequence is written to a specific location in the AFE's command SRAM (e.g., Sequence ID 0).

+**2** **Configure Sequence B:** A second sequence is created with a single SEQ_STOP() command. This command halts the sequencer and generates an END_SEQ interrupt, signaling the host microcontroller that a measurement period is complete. This sequence is written to another SRAM location (e.g., Sequence ID 1).

+**3** **Write Sequences to SRAM:** Both sequences are loaded into the AFE's onboard SRAM.

+**4** **Configure the Wakeup Timer:** The wakeup timer is configured to execute Sequence A first, then Sequence B, with a specific time duration (CalDuration) between them.

+**5** **Run First Measurement:** The wakeup timer is enabled. It triggers Sequence A, which starts the timeout counter. After the specified CalDuration (e.g., 1000 ms), the timer triggers Sequence B. The END_SEQ interrupt from Sequence B prompts the host MCU to read the final count from the **SEQTIMEOUT** register. This value (TimerCount) represents the wakeup period plus the time required for the MCU to read the register.

+**6** **Measure Read Latency:** Sequence B is reconfigured to reset the timeout counter before generating the END_SEQ interrupt. It is then run again. This time, the value read back by the host (TimerCount2) represents only the time it takes to read the register.

+**7** **Calculate Frequency:** The final LFOSC frequency is calculated using the difference between TimerCount and TimerCount2, along with the known system clock frequency.

+

+⠀**11.3 Frequency Calculation**

+***Editor's Note:*** *The formula presented in the original source documentation for this calculation appears to be erroneous, simplifying to a physically impossible result. The formula below has been corrected to reflect the logical intent of the calibration procedure.*

+The frequency of the low-frequency oscillator is calculated by determining how many system clock cycles occur during a known number of LFOSC cycles (CalDuration_in_ticks). The corrected formula is:

+### Frequency = (CalDuration_in_ticks * SystemClkFreq) / (TimerCount - TimerCount2)

+Where:

+* **Frequency**: The calculated Low Frequency Oscillator frequency in Hz.

+* **CalDuration_in_ticks**: The length of the calibration period, specified in LFOSC clock ticks.

+* **SystemClkFreq**: The frequency of the AD5940 system clock in Hz (ideally 16 MHz from an external crystal for highest accuracy).

+* **TimerCount**: The value read from the **SEQTIMEOUT** register after the first measurement.

+* **TimerCount2**: The value read from the **SEQTIMEOUT** register after the second (latency) measurement.

+* **(TimerCount - TimerCount2)**: This difference represents the total number of system clock cycles that elapsed during the CalDuration period.

+

+⠀**11.4 SDK Implementation Note**

+The AD5940 Software Development Kit (SDK) provides a ready-to-use function, AD5940_LFOSCMeasure(), which encapsulates this entire calibration logic. This function simplifies the process for the developer and takes key input parameters to control the measurement:

+* **CalDuration**: Sets the length of the calibration routine (a value of 1000 ms is advisable for accuracy).

+* **SystemClkFreq**: Sets the system clock frequency, which should be 16 MHz for best results.

+

+⠀By performing this calibration, applications can achieve a high level of accuracy in their measurement sampling frequency, which is critical for time-sensitive electrochemical analysis.

+

+

diff --git a/CMakeLists.txt b/CMakeLists.txt

index f09e630..7f25ce6 100644

--- a/CMakeLists.txt

+++ b/CMakeLists.txt

@@ -1,6 +1,4 @@

-# The following five lines of boilerplate have to be in your project's

-# CMakeLists in this exact order for cmake to work correctly

-cmake_minimum_required(VERSION 3.16)

+cmake_minimum_required(VERSION 3.5)

include($ENV{IDF_PATH}/tools/cmake/project.cmake)

-project(AutoSpa)

+project(ad5940_webserver)

diff --git a/components/ad5940/CMakeLists.txt b/components/ad5940/CMakeLists.txt

new file mode 100644

index 0000000..3ff5aff

--- /dev/null

+++ b/components/ad5940/CMakeLists.txt

@@ -0,0 +1,4 @@

+idf_component_register(SRCS "ad5940.c"

+ INCLUDE_DIRS ".")

+

+target_compile_options(${COMPONENT_LIB} PRIVATE -w)

diff --git a/components/ad5940/ad5940.c b/components/ad5940/ad5940.c

new file mode 100644

index 0000000..e4165d3

--- /dev/null

+++ b/components/ad5940/ad5940.c

@@ -0,0 +1,4422 @@

+/**

+ * @file ad5940.c

+ * @brief AD5940 library. This file contains all AD5940 library functions.

+ * @author ADI

+ * @date March 2019

+ * @par Revision History:

+ *

+ * Copyright (c) 2017-2019 Analog Devices, Inc. All Rights Reserved.

+ *

+ * This software is proprietary to Analog Devices, Inc. and its licensors.

+ * By using this software you agree to the terms of the associated

+ * Analog Devices Software License Agreement.

+**/

+#include "ad5940.h"

+

+/*! \mainpage AD5940 Library Introduction

+ *

+ *

+ *

+ * # Introduction

+ *

+ * The documentation is for AD594x library and examples.

+ *

+ * # Manual Structure

+ *

+ * @ref AD5940_Library

+ * - @ref AD5940_Functions

+ * - @ref TypeDefinitions

+ * @ref AD5940_Standard_Examples

+ * @ref AD5940_System_Examples

+ *

+ * # How to Use It

+ * We provide examples that can directly run out of box.

+ * The files can generally be separated to three parts:

+ * - AD5940 Library files. ad5940.c and ad5940.h specifically. These two files are shared among all examples.

+ * - AD5940 System Examples. The system examples mean system level application like measuring impedance.

+ * - Standard examples. These include basic block level examples like ADC. It shows how to setup and use one specific block.

+ *

+ * ## Requirements to run these examples

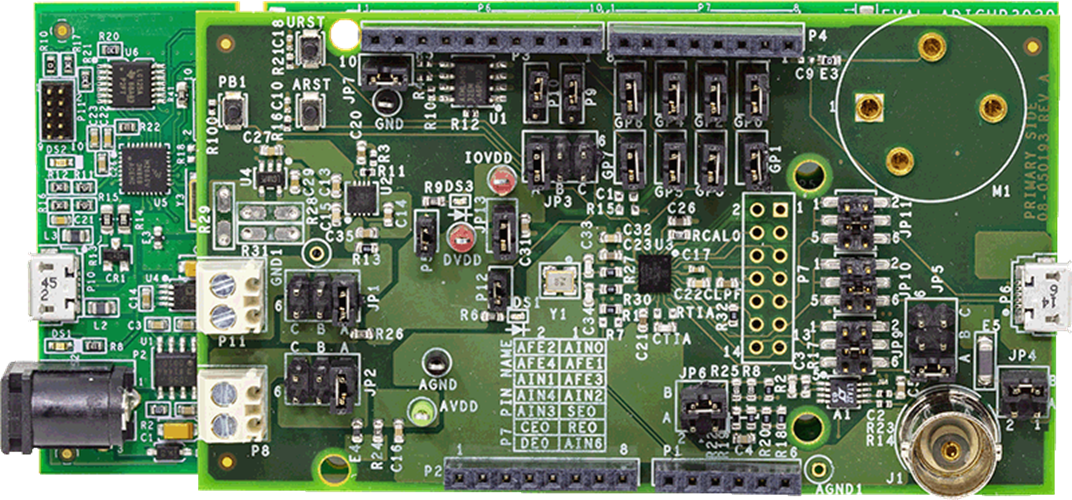

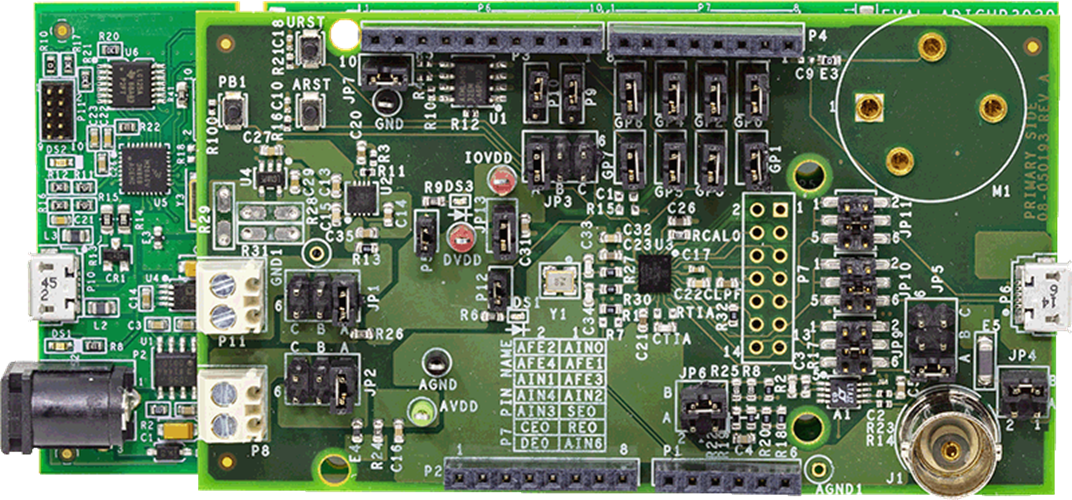

+ * ### Hardware

+ * - Use EVAL_AD5940 or EVAL_AD5941. The default MCU board we used is ADICUP3029. We also provide project for ST NUCLEO board.

+ * - Or use EVAL_ADuCM355

+ * ### Software

+ * - Pull all the source file from [GitHub](https://github.com/analogdevicesinc/ad5940-examples.git)

+ * - CMSIS pack that related to specific MCU. This normally is done by IDE you use.

+ *

+ * ## Materials

+ * Please use this library together with following materials.

+ * - [AD5940 Data Sheet](https://www.analog.com/media/en/technical-documentation/data-sheets/AD5940.pdf)

+ * - [AD5940 Eval Board](https://www.analog.com/en/design-center/evaluation-hardware-and-software/evaluation-boards-kits/EVAL-AD5940.html)

+ *

+ */

+

+/* Remove below variables after AD594x is released. */

+static BoolFlag bIsS2silicon = bFALSE;

+

+/* Declare of SPI functions used to read/write registers */

+#ifndef CHIPSEL_M355

+static uint32_t AD5940_SPIReadReg(uint16_t RegAddr);

+static void AD5940_SPIWriteReg(uint16_t RegAddr, uint32_t RegData);

+#else

+static uint32_t AD5940_D2DReadReg(uint16_t RegAddr);

+static void AD5940_D2DWriteReg(uint16_t RegAddr, uint32_t RegData);

+#endif

+

+/**

+ * @addtogroup AD5940_Library

+ * The library functions, structures and constants.

+ * @{

+ * @defgroup AD5940_Functions

+ * @{

+ * @defgroup Function_Helpers

+ * @brief The functions with no hardware access. They are helpers.

+ * @{

+ * @defgroup Sequencer_Generator_Functions

+ * @brief The set of function used to track all register read and write once it's enabled. It can translate register write operation to sequencer commands.

+ * @{

+*/

+

+#define SEQUENCE_GENERATOR /*!< Build sequence generator part in to lib. Comment this line to remove this feature */

+

+#ifdef SEQUENCE_GENERATOR

+/**

+ * Structure used to store register information(address and its data)

+ * */

+typedef struct

+{

+ uint32_t RegAddr :8; /**< 8bit address is enough for sequencer */

+ uint32_t RegValue :24; /**< Reg data is limited to 24bit by sequencer */

+}SEQGenRegInfo_Type;

+

+/**

+ * Sequencer generator data base.

+*/

+struct

+{

+ BoolFlag EngineStart; /**< Flag to mark start of the generator */

+ uint32_t BufferSize; /**< Total buffer size */

+

+ uint32_t *pSeqBuff; /**< The buffer for sequence generator(both sequences and RegInfo) */

+ uint32_t SeqLen; /**< Generated sequence length till now */

+ SEQGenRegInfo_Type *pRegInfo; /**< Pointer to buffer where stores register info */

+ uint32_t RegCount; /**< The count of register info available in buffer *pRegInfo. */

+ AD5940Err LastError; /**< The last error message. */

+}SeqGenDB; /* Data base of Seq Generator */

+

+/**

+ * @brief Manually input a command to sequencer generator.

+ * @param CmdWord: The 32-bit width sequencer command word. @ref Sequencer_Helper can be used to generate commands.

+ * @return None;

+*/

+void AD5940_SEQGenInsert(uint32_t CmdWord)

+{

+ uint32_t temp;

+ temp = SeqGenDB.RegCount + SeqGenDB.SeqLen;

+ /* Generate Sequence command */

+ if(temp < SeqGenDB.BufferSize)

+ {

+ SeqGenDB.pSeqBuff[SeqGenDB.SeqLen] = CmdWord;

+ SeqGenDB.SeqLen ++;

+ }

+ else /* There is no buffer */

+ SeqGenDB.LastError = AD5940ERR_BUFF;

+}

+

+/**

+ * @brief Search data-base to get current register value.

+ * @param RegAddr: The register address.

+ * @param pIndex: Pointer to a variable that used to store index of found register-info.

+ * @return Return AD5940ERR_OK if register found in data-base. Otherwise return AD5940ERR_SEQREG.

+*/

+static AD5940Err AD5940_SEQGenSearchReg(uint32_t RegAddr, uint32_t *pIndex)

+{

+ uint32_t i;

+

+ RegAddr = (RegAddr>>2)&0xff;

+ for(i=0;i>2)&0xff;

+ SeqGenDB.pRegInfo[0].RegValue = RegData&0x00ffffff;

+ SeqGenDB.RegCount ++;

+ }

+ else /* There is no more buffer */

+ {

+ SeqGenDB.LastError = AD5940ERR_BUFF;

+ }

+}

+

+/**

+ * @brief Get current register value. If we have record in data-base, read it. Otherwise, return the register default value.

+ * @param RegAddr: The register address.

+ * @return Return register value.

+*/

+static uint32_t AD5940_SEQReadReg(uint16_t RegAddr)

+{

+ uint32_t RegIndex, RegData;

+

+ if(AD5940_SEQGenSearchReg(RegAddr, &RegIndex) != AD5940ERR_OK)

+ {

+ /* There is no record in data-base, read the default value. */

+ AD5940_SEQGenGetRegDefault(RegAddr, &RegData);

+ AD5940_SEQRegInfoInsert(RegAddr, RegData);

+ }

+ else

+ {

+ /* return the current register value stored in data-base */

+ RegData = SeqGenDB.pRegInfo[RegIndex].RegValue;

+ }

+

+ return RegData;

+}

+

+/**

+ * @brief Generate a sequencer command to write register. If the register address is out of range, it won't generate a command.

+ * This function will also update the register-info in data-base to record current register value.

+ * @param RegAddr: The register address.

+ * @param RegData: The register value.

+ * @return Return None.

+*/

+static void AD5940_SEQWriteReg(uint16_t RegAddr, uint32_t RegData)

+{

+ uint32_t RegIndex;

+

+ if(RegAddr > 0x21ff)

+ {

+ SeqGenDB.LastError = AD5940ERR_ADDROR; /* address out of range */

+ return;

+ }

+

+ if(AD5940_SEQGenSearchReg(RegAddr, &RegIndex) == AD5940ERR_OK)

+ {

+ /* Store register value */

+ SeqGenDB.pRegInfo[RegIndex].RegValue = RegData;

+ /* Generate Sequence command */

+ AD5940_SEQGenInsert(SEQ_WR(RegAddr, RegData));

+ }

+ else

+ {

+ AD5940_SEQRegInfoInsert(RegAddr, RegData);

+ /* Generate Sequence command */

+ AD5940_SEQGenInsert(SEQ_WR(RegAddr, RegData));

+ }

+}

+

+/**

+ * @brief Initialize sequencer generator with specified buffer.

+ * The buffer is used to store sequencer generated and record register value changes.

+ * The command is stored from start address of buffer while register value is stored from end of buffer.

+ * Buffer[0] : First sequencer command;

+ * Buffer[1] : Second Sequencer command;

+ * ...

+ * Buffer[Last-1]: The second register value record.

+ * Buffer[Last]: The first register value record.

+ * @param pBuffer: Pointer to the buffer.

+ * @param BufferSize: The buffer length.

+ * @return Return None.

+*/

+void AD5940_SEQGenInit(uint32_t *pBuffer, uint32_t BufferSize)

+{

+ if(BufferSize < 2) return;

+ SeqGenDB.BufferSize = BufferSize;

+ SeqGenDB.pSeqBuff = pBuffer;

+ SeqGenDB.pRegInfo = (SEQGenRegInfo_Type*)pBuffer + BufferSize - 1; /* Point to the last element in buffer */

+ SeqGenDB.SeqLen = 0;

+

+ SeqGenDB.RegCount = 0;

+ SeqGenDB.LastError = AD5940ERR_OK;

+ SeqGenDB.EngineStart = bFALSE;

+}

+

+/**

+ * @brief Get sequencer command generated.

+ * @param ppSeqCmd: Pointer to a variable(pointer) used to store the pointer to generated sequencer command.

+ * @param pSeqLen: Pointer to a variable that used to store how many commands available in buffer.

+ * @return Return lasterror.

+*/

+AD5940Err AD5940_SEQGenFetchSeq(const uint32_t **ppSeqCmd, uint32_t *pSeqLen)

+{

+ AD5940Err lasterror;

+

+ if(ppSeqCmd)

+ *ppSeqCmd = SeqGenDB.pSeqBuff;

+ if(pSeqLen)

+ *pSeqLen = SeqGenDB.SeqLen;

+

+ //SeqGenDB.SeqLen = 0; /* Start a new sequence */

+ lasterror = SeqGenDB.LastError;

+ //SeqGenDB.LastError = AD5940ERR_OK; /* Clear error message */

+ return lasterror;

+}

+

+/**

+ * @brief Start or stop the sequencer generator. Once started, the register write will be recorded to sequencer generator.

+ * Once it's disabled, the register write is written to AD5940 directly by SPI bus.

+ * @param bFlag: Enable or disable sequencer generator.

+ * @return Return None.

+*/

+void AD5940_SEQGenCtrl(BoolFlag bFlag)

+{

+ if(bFlag == bFALSE) /* Disable sequence generator */

+ {

+ SeqGenDB.EngineStart = bFALSE;

+ }

+ else

+ {

+ SeqGenDB.SeqLen = 0;

+ SeqGenDB.LastError = AD5940ERR_OK; /* Clear error message */

+ SeqGenDB.EngineStart = bTRUE;

+ }

+}

+

+/**

+ * @brief Calculate the number of cycles in the sequence

+ * @return Return Number of ACLK Cycles that a generated sequence will take.

+*/

+uint32_t AD5940_SEQCycleTime(void)

+{

+ uint32_t i, Cycles, Cmd;

+ Cycles = 0;

+ for(i=0;i> 30) & 0x3;

+ if (Cmd & 0x2)

+ {

+ /* A write command */

+ Cycles += 1;

+ }

+ else

+ {

+ if (Cmd & 0x1)

+ {

+ /* Timeout Command */

+ Cycles += 1;

+ }

+ else

+ {

+ /* Wait command */

+ Cycles += SeqGenDB.pSeqBuff[i] & 0x3FFFFFFF;

+ }

+ }

+ }

+ return Cycles;

+}

+#endif

+/**

+ * @} Sequencer_Generator_Functions

+*/

+

+/**

+ * Check if an uint8_t value exist in table.

+*/

+static int32_t _is_value_in_table(uint8_t value, const uint8_t *table, uint8_t len, uint8_t *index)

+{

+ for(int i=0; iADCRate == ADCRATE_800KHZ && pFilterInfo->ADCSinc3Osr == ADCSINC3OSR_2)||\

+ (pFilterInfo->ADCRate == ADCRATE_1P6MHZ && pFilterInfo->ADCSinc3Osr != ADCSINC3OSR_2))

+ {

+ //this combination suits for filter:

+ //SINC3 OSR2, for 800kSPS

+ //and SINC3 OSR4 and OSR5 for 1.6MSPS,

+ const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_533, ADCSINC2OSR_667,ADCSINC2OSR_800, ADCSINC2OSR_889, ADCSINC2OSR_1333};

+ const uint8_t dl_50Hz[] = {15,12,10,9,6};

+ uint8_t index;

+ if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

+ {

+ *dl = dl_50Hz[index];

+ return bTRUE;

+ }

+ }

+ else if(pFilterInfo->ADCRate == ADCRATE_1P6MHZ && pFilterInfo->ADCSinc3Osr == ADCSINC3OSR_2)

+ {

+ //this combination suits for filter:

+ //SINC3 OSR2 for 1.6MSPS

+ const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_889, ADCSINC2OSR_1067, ADCSINC2OSR_1333};

+ const uint8_t dl_50Hz[] = {18,15,12};

+ uint8_t index;

+ if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

+ {

+ *dl = dl_50Hz[index];

+ return bTRUE;

+ }

+ }

+ else if(pFilterInfo->ADCRate == ADCRATE_800KHZ && pFilterInfo->ADCSinc3Osr != ADCSINC3OSR_2)

+ {

+ //this combination suits for filter:

+ //SINC3 OSR4 and OSR5 for 800kSPS,

+ const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_178, ADCSINC2OSR_267, ADCSINC2OSR_533, ADCSINC2OSR_640,\

+ ADCSINC2OSR_800, ADCSINC2OSR_1067};

+ const uint8_t dl_50Hz[] = {18,12,6,5,4,3};

+ uint8_t index;

+ if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

+ {

+ *dl = dl_50Hz[index];

+ return bTRUE;

+ }

+ }

+ *dl = 0;

+ return bFALSE;

+}

+

+/**

+ * @brief return if the SINC3/SINC2 combination is available for notch 60Hz filter.

+ * If it's not availabe, hardware automatically bypass Notch even if it's enabled.

+ * @param pFilterInfo the filter configuration, need sinc2/sinc3 osr and adc data rate information.

+ * @return return bTRUE if notch 60Hz filter is available.

+*/

+BoolFlag AD5940_Notch60HzAvailable(ADCFilterCfg_Type *pFilterInfo, uint8_t *dl)

+{

+ if((pFilterInfo->ADCRate == ADCRATE_800KHZ && pFilterInfo->ADCSinc3Osr == ADCSINC3OSR_2)||\

+ (pFilterInfo->ADCRate == ADCRATE_1P6MHZ && pFilterInfo->ADCSinc3Osr != ADCSINC3OSR_2))

+ {

+ //this combination suits for filter:

+ //SINC3 OSR2, for 800kSPS

+ //and SINC3 OSR4 and OSR5 for 1.6MSPS,

+ const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_667, ADCSINC2OSR_1333};

+ const uint8_t dl_60Hz[] = {10,5};

+ uint8_t index;

+ if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

+ {

+ *dl = dl_60Hz[index];

+ return bTRUE;

+ }

+ }

+ else if(pFilterInfo->ADCRate == ADCRATE_1P6MHZ && pFilterInfo->ADCSinc3Osr == ADCSINC3OSR_2)

+ {

+ //this combination suits for filter:

+ //SINC3 OSR2 for 1.6MSPS

+ const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_889, ADCSINC2OSR_1333};

+ const uint8_t dl_60Hz[] = {15,10};

+ uint8_t index;

+ if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

+ {

+ *dl = dl_60Hz[index];

+ return bTRUE;

+ }

+ }

+ else if(pFilterInfo->ADCRate == ADCRATE_800KHZ && pFilterInfo->ADCSinc3Osr != ADCSINC3OSR_2)

+ {

+ //this combination suits for filter:

+ //SINC3 OSR4 and OSR5 for 800kSPS,

+ const uint8_t available_sinc2_osr[] = {ADCSINC2OSR_178, ADCSINC2OSR_267, ADCSINC2OSR_533, ADCSINC2OSR_667,\

+ ADCSINC2OSR_889, ADCSINC2OSR_1333};

+ const uint8_t dl_60Hz[] = {15,10,5,4,3,2};

+ uint8_t index;

+ if(_is_value_in_table(pFilterInfo->ADCSinc2Osr, available_sinc2_osr, sizeof(available_sinc2_osr), &index))

+ {

+ *dl = dl_60Hz[index];

+ return bTRUE;

+ }

+ }

+ *dl = 0;

+ return bFALSE;

+}

+

+/**

+ * @brief Calculate how many clocks are needed in sequencer wait command to generate required number of data from filter output.

+ * @note When measurement is done, it's recommend to disable blocks like ADCPWR, ADCCNV, SINC2, DFT etc. If blocks remain powered up,

+ * they may need less clocks to generate required number of output. Use function @ref AD5940_AFECtrlS to control these blocks.

+ * @param pFilterInfo: Pointer to configuration structure.

+ * @param pClocks: pointer used to store results.

+ * @return return none.

+*/

+void AD5940_ClksCalculate(ClksCalInfo_Type *pFilterInfo, uint32_t *pClocks)

+{

+ uint32_t temp = 0;

+ const uint32_t sinc2osr_table[] = {22,44,89,178,267,533,640,667,800,889,1067,1333,0};

+ const uint32_t sinc3osr_table[] = {5,4,2,0};

+

+ *pClocks = 0;

+ if(pFilterInfo == NULL) return;

+ if(pClocks == NULL) return;

+ if(pFilterInfo->ADCSinc2Osr > ADCSINC2OSR_1333) return;

+ if(pFilterInfo->ADCSinc3Osr > 2) return; /* 0: OSR5, 1:OSR4, 2:OSR2 */

+ if(pFilterInfo->ADCAvgNum > ADCAVGNUM_16) return; /* Average number index:0,1,2,3 */

+ switch(pFilterInfo->DataType)

+ {

+ case DATATYPE_ADCRAW:

+ temp = (uint32_t)(20*pFilterInfo->DataCount*pFilterInfo->RatioSys2AdcClk);

+ break;

+ case DATATYPE_SINC3:

+ temp = (uint32_t)(((pFilterInfo->DataCount+2)*sinc3osr_table[pFilterInfo->ADCSinc3Osr]+1)*20*pFilterInfo->RatioSys2AdcClk + 0.5f);

+ break;

+ case DATATYPE_SINC2:

+ temp = (pFilterInfo->DataCount+1)*sinc2osr_table[pFilterInfo->ADCSinc2Osr] + 1;

+ pFilterInfo->DataType = DATATYPE_SINC3;

+ pFilterInfo->DataCount = temp;

+ AD5940_ClksCalculate(pFilterInfo, &temp);

+ pFilterInfo->DataType = DATATYPE_SINC2;

+ temp += 15; /* Need extra 15 clocks for FIFO etc. Just to be safe. */

+ break;

+ case DATATYPE_NOTCH:

+ {

+ ADCFilterCfg_Type filter;

+ filter.ADCRate = pFilterInfo->ADCRate;

+ filter.ADCSinc3Osr = pFilterInfo->ADCSinc3Osr;

+ filter.ADCSinc2Osr = pFilterInfo->ADCSinc2Osr;

+ uint8_t dl=0, dl_50, dl_60;

+ if(AD5940_Notch50HzAvailable(&filter, &dl_50)){

+ dl += dl_50 - 1;

+ }

+ if(AD5940_Notch60HzAvailable(&filter, &dl_60)){

+ dl += dl_60 - 1;

+ }

+ pFilterInfo->DataType = DATATYPE_SINC2;

+ pFilterInfo->DataCount += dl; //DL is the extra data input needed for filter to output first data.

+ AD5940_ClksCalculate(pFilterInfo,&temp);

+ //restore the filter info.

+ pFilterInfo->DataType = DATATYPE_NOTCH;

+ pFilterInfo->DataCount -= dl;

+ break;

+ }

+ case DATATYPE_DFT:

+ switch(pFilterInfo->DftSrc)

+ {

+ case DFTSRC_ADCRAW:

+ pFilterInfo->DataType = DATATYPE_ADCRAW;

+ AD5940_ClksCalculate(pFilterInfo, &temp);

+ break;

+ case DFTSRC_SINC3:

+ pFilterInfo->DataType = DATATYPE_SINC3;

+ AD5940_ClksCalculate(pFilterInfo, &temp);

+ break;

+ case DFTSRC_SINC2NOTCH:

+ if(pFilterInfo->BpNotch)

+ pFilterInfo->DataType = DATATYPE_SINC2;

+ else

+ pFilterInfo->DataType = DATATYPE_NOTCH;

+ AD5940_ClksCalculate(pFilterInfo, &temp);

+ break;

+ case DFTSRC_AVG:

+ pFilterInfo->DataType = DATATYPE_SINC3;

+ pFilterInfo->DataCount *= 1L<<(pFilterInfo->ADCAvgNum+1); /* 0: average2, 1: average4, 2: average8, 3: average16 */

+ AD5940_ClksCalculate(pFilterInfo, &temp);

+ break;

+ default:

+ break;

+ }

+ pFilterInfo->DataType = DATATYPE_DFT;

+ temp += 25; /* add margin */

+ break;

+ default:

+ break;

+ }

+ *pClocks = temp;

+}

+

+/**

+ @brief void AD5940_SweepNext(SoftSweepCfg_Type *pSweepCfg, float *pNextFreq)

+ For sweep function, calculate next frequency point according to pSweepCfg info.

+ @return Return next frequency point in Hz.

+*/

+void AD5940_SweepNext(SoftSweepCfg_Type *pSweepCfg, float *pNextFreq)

+{

+ float frequency;

+

+ if(pSweepCfg->SweepLog)/* Log step */

+ {

+ if(pSweepCfg->SweepStartSweepStop) /* Normal */

+ {

+ if(++pSweepCfg->SweepIndex == pSweepCfg->SweepPoints)

+ pSweepCfg->SweepIndex = 0;

+ frequency = pSweepCfg->SweepStart*pow(10,pSweepCfg->SweepIndex*log10(pSweepCfg->SweepStop/pSweepCfg->SweepStart)/(pSweepCfg->SweepPoints-1));

+ }

+ else

+ {

+ pSweepCfg->SweepIndex --;

+ if(pSweepCfg->SweepIndex >= pSweepCfg->SweepPoints)

+ pSweepCfg->SweepIndex = pSweepCfg->SweepPoints-1;

+ frequency = pSweepCfg->SweepStop*pow(10,pSweepCfg->SweepIndex*

+ (log10(pSweepCfg->SweepStart/pSweepCfg->SweepStop)/(pSweepCfg->SweepPoints-1)));

+ }

+ }

+ else/* Linear step */

+ {

+ if(pSweepCfg->SweepStartSweepStop) /* Normal */

+ {

+ if(++pSweepCfg->SweepIndex == pSweepCfg->SweepPoints)

+ pSweepCfg->SweepIndex = 0;

+ frequency = pSweepCfg->SweepStart + pSweepCfg->SweepIndex*(double)(pSweepCfg->SweepStop-pSweepCfg->SweepStart)/(pSweepCfg->SweepPoints-1);

+ }

+ else

+ {

+ pSweepCfg->SweepIndex --;

+ if(pSweepCfg->SweepIndex >= pSweepCfg->SweepPoints)

+ pSweepCfg->SweepIndex = pSweepCfg->SweepPoints-1;

+ frequency = pSweepCfg->SweepStop + pSweepCfg->SweepIndex*(double)(pSweepCfg->SweepStart - pSweepCfg->SweepStop)/(pSweepCfg->SweepPoints-1);

+ }

+ }

+

+ *pNextFreq = frequency;

+}

+

+/**

+ @brief Initialize Structure members to zero

+ @param pStruct: Pointer to the structure.

+ @param StructSize: The structure size in Byte.

+ @return Return None.

+**/

+void AD5940_StructInit(void *pStruct, uint32_t StructSize)

+{

+ memset(pStruct, 0, StructSize);

+}

+

+/**

+ @brief Convert ADC Code to voltage.

+ @param ADCPga: The ADC PGA used for this result.

+ @param code: ADC code.

+ @param VRef1p82: the actual 1.82V reference voltage.

+ @return Voltage in volt.

+**/

+float AD5940_ADCCode2Volt(uint32_t code, uint32_t ADCPga, float VRef1p82)

+{

+ float kFactor = 1.835/1.82;

+ float fVolt = 0.0;

+ float tmp = 0;

+ tmp = (int32_t)code - 32768;

+ switch(ADCPga)

+ {

+ case ADCPGA_1: